下面以Altera的Stratix GX FPGA为例介绍其中的内嵌的数千兆位收发器功能块。

Stratix GX器件将高速3.125Gbit/s收发器串行/解串行(SERDES)技术和业界最先进的FPGA架构相结合。在FPGA中嵌入的数千兆位收发器功能块,能够在需要灵活性、高性能和最先进功能的许多新系统中使用收发器。

下面是这个数千兆位收发器功能块的主要特点。

·支持从622MHz~3.125GHz的所有频率。

·每个块有4个独立的3.125Gbit/s全双工通道,每个器件多达20个通道(5个块)。

·支持3.1875Gbit/s的10Gbit光纤通道。

·集成时钟数据恢复(CDR)、模式检测、字对齐、8b/10b编解码器和同步功能。

·功耗很低,每4通道只有450mW(包括数千兆收发器功能块的功耗)。

·支持动态可编程:预加重、均衡和I/O缓冲上的差分输出电压。

·支持SerialLite协议,这是一个精简的点对点协议。

·对中等性能信号的差分片内匹配。

·完全实现10Gbit以太网物理介质接入层(PMA)和物理编码子层(PCS)功能。

·支持灵活的时钟拓扑,每个收发器模块中有一个发送器PLL和四个接收器PLL。

·采用1.5V、0.13mm全铜CMOS工艺技术制造,支持1.5V PCML I/O标准。

·包括独立的发送器和接收器节电功能,在不工作过程中减小功耗。

·内嵌自检(BIST)功能,包括嵌入伪随机二进制序列(PRBS)图案生成和验证。

·有4个独立的环回路径用于系统验证。

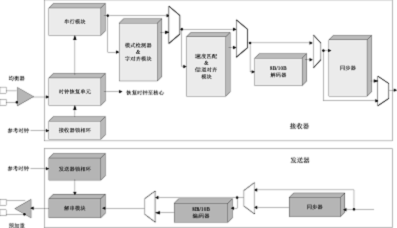

可以看到,Stratix GX的这个收发器功能非常强大,远远超出了图9.39所示的SERDES基本结构图的功能。图9.40是它的原理框图,需要说明的是,设计者在使用这个模块时并不一定完全实现其中的每一个模块,可以根据需要只实现其中的部分内容。

图9.40Stratix GX收发机

下面介绍其中的一些模块。

(1)差分缓冲。

数千兆位收发器功能块差分I/O缓冲支持1.5V PCML I/O标准,有许多改善系统信号完整性的特性。例如,动态可重配置预加重和均衡功能,调整信号以补偿信号经过传送介质的衰减。不同的可编程VOD设置确保了驱动强度匹配传输线电阻和线长。另外,差分片内匹配为中等性能信号提供了合适的接收器和发送器缓冲匹配。

(2)可编程发送预加重模块。

发送预加重块使收发器(SERDES)可以驱动更长的背板或超过1GHz频率下的电缆。在这些频率下,通道损耗是很高的,衰减是很明显的,因为眼图的关闭无法让发送的信号继续传送。预加重信号提升信号的高频部分,补偿传输线的衰减。使用可编程的预加重设置,能够为给定的传输线选择最优的水平(或者在软件设定,或者通过内部或外部信号动态选择),让信号眼图在远端张得最开。

(3)可编程接收均衡器模块。

接收均衡器块使得收发器(SERDES)驱动更长的背板或超过1GHz的电缆。当信号经过接收器均衡器块时,同样可以提升信号的高频部分能量,补偿传输线的高频衰减指标。可编程均衡水平可以根据传输线进行优化(或者在软件设定或者通过内部或外部信号动态选择),让信号眼图在CDR单元输入端张得最开。

(4)发送器和接收器PLL。

每个数千兆位收发器功能块有一个专用发送器PLL和四个专用接收器PLL,提供灵活的时钟拓扑,支持一系列的输入数据流。对于输出传送和接收,这些PLL根据更低速的输入参考时钟生成所需的时钟频率。每个PLL支持4、8、10、16或20的倍增因子。每个外部参考时钟或Stratix GX内的各种时钟源都可以驱动PLL。

(5)时钟恢复单元。

CDR从输入串行数据流中提取时钟。恢复的时钟用于采样串行数据流、同步控制解串行器。

(6)串行/解串模块。

SERDES模块将输入的高速串行数据转换为更低速度的并行接口,反之亦然。SERDES模块可以配置为8、10、16或20位并行接口。

(7)模式检测器模块。

模式检测器模块识别输入数据流中的特殊模式。模式检测器包括一个内建的8b/10b的K28间隔符号检测和SONET的A1A2模式检测。在定制模式下,设计者可以创建专用模式。

(8)字对齐模块。

字对齐模块和模式检测器共同识别和调整正确的字节边界。此外,字对齐有一个定制模式,能够从FPGA内核逻辑人工地控制字节对齐。

(9)速率匹配器模块。

在串行数据传输中,发送和接收器件的时钟频率通常是不匹配的。这种不匹配会引起数据以略快或慢于接收器件能解释的速度传送。Stratix GX速率匹配器从数据流中插入或删除如传送协议中定义的可移除的符号,解决了恢复时钟和PLD逻辑阵列时钟的频差,而不会丢失传送的数据。Stratix GX数据匹配器为使用8b/10b编码数据的系统进行了优化。

(10)信道对齐器。

信道对齐器消除了实现4个收发器XAUI协议相关的信道至信道的偏移。信道对齐器消除4信道的偏移,为内核逻辑建立了可靠的以太网XGMII接口。

(11)8b/10b编解码器。

8b/10b编解码器模块将8比特的数据转换为10比特的数据,反之亦然。该算法平衡了串行数据流中“0”和“1”的数量,增加了变换密度,因此更易于接收器恢复串行数据。

(12)同步器。

同步器补偿了并行收发器接口和FPGA内核逻辑之间的相位差。

(13)内建自测。

BIST为收发器提供了一组强大的诊断能力。它包括伪随机二进制序列(PRBS)和其他图案的生成器和检查器。BIST也提供了4个环回配置用于系统诊断 |