基于TMS320C6678的多核DSP上电加载技术

|

- UID

- 872339

|

基于TMS320C6678的多核DSP上电加载技术

0 引言

在视频检测、医疗影像及红外图像快速跟瞄系统应用中,越来越复杂的二维、三维甚至四维的图像处理,需要并行化的处理系统,并能够运行复杂的算法。要实现这些复杂的系统,高端FPGA+高性能DSP是目前普遍采用的方案,而单个DSP的性能已发展至极限,所以解决复杂的并行算法,多核DSP是现在发展的全新方向,其中多核DSP的根加载技术是其难点之一。

TI公司推出的DSP芯片TMS320C6678(C6678)具有8个内核的高性能DSP,每个内核工作频率均达1 GHz。

其支持的Boot 模式有SPI、I2C、EMAC、SRIO 和并口Emif16 NOR-FLASH。其中Emif16 NOR-FLASH模式是不用上位机参与、比较简单、独立成系统的一种,大多独立DSP系统采用该方式。

网上能搜索到关于C6472和C6678零星一些加载资料,都是借助于第三方转换工具,太过于笼统。下面是针对C6678 的并口Emif16NOR-FLASH的上电加载作详细的探讨。

1 C6678 的上电加载过程

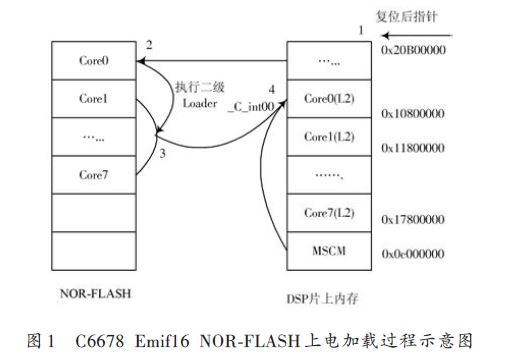

所谓上电加载(上电自举),即是当DSP复位后,正常运行用户程序之前运行的一段小程序,就像PC机的BIOS 一样。多核加载同单核加载区别很大,不但要负责主核的加载而且还有其他核的加载与激活。C6678的Emif16 NOR-FLASH 可以直接执行程序(XIP)(这与C641x系列DSP不同),其上电加载过程示于图1。

上电复位后,DSP 首先运行固化在片上ROM位于地址0x20b00000的程序,称为片上Loader,片上Loader根据DSP硬件管脚状态,判断用户采用的Boot模式以跳转到相应模式的二级加载程序。如图1的 Emif16 NOR-FLASH模式中,运行片上Loader后,PC指针直接指向NOR-FLASH首地址0×70000000并开始执行FLASH上的二级Loader程序,二级Loader存储在FLASH开始地址0×70000000~0×70000400的范围内。从0×70000400开始保存应用程序的根表数据(即被烧烧写到FLASH中的应用程序的数据)。二级Loader的功能是将保存在 FLASH中的Core0~Core7的根表数据搬移到DSP相应的地址段内,搬移完后,二级Loader程序PC指针跳到Core0的主程序入口地址_c_int00处,开始执行Core0的应用程序。在Core0的应用程序开始加有使其他核激活运行的代码(这也是有别于单核的特殊之处),至此整个多核加载就此完成。事实上,如果你的应用程序很小,且运行速度要求不高,图1中的2、3和4过程都可以不要,只要把应用程序的原始代码数据烧写到FLASH从0×70000000开始的位置,上电正常运行即可(这在C641x 上是不行的),如此DSP 的许多高性能就体现不出来,且多核工程大多采用嵌入式sysbios工程,占用存储器比较大,所以正常的Boot过程必须采用图1所示的二级加载过程。

从图1中看出,一个完整多核加载过程,开发者需要做的是二级加载器Loader的编写、FLASH中映像文件的产生、FLASH烧写器的编写,主核对各辅助核的触发代码的编写(被加载的应用程序不在本范围内)。

|

|

|

|

|

|