|

- UID

- 1029342

- 性别

- 男

|

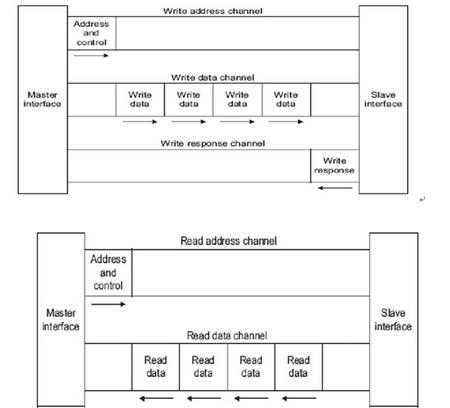

1、AXI总线将写地址通道、写数据通道、写响应通道、读地址通道、读数据通道分开,这是AXI总线效率比较高的一个原因,类似于全双工的感觉,每个通道互不干扰却又彼此依赖;但是为什么写会出现三个通道,但是读却只有两个通道呢,那是因为读将读数据通道和读响应通道合并成了读数据通道,因为读数据和读响应都由slave发出,当最后一笔数据被读出的时候,slave完全可以在这个时候给出当前这个burst读状态(例如是ok还是error),但是写就不同了,虽然写数据可能已经被slave接收了,但是接收完最后一笔数据的时候,slave可能不能及时反馈当前这个burst是否写成功,因为数据可能并没有完全到达目的地;而且写成功与否肯定是slave应答,所以单独开辟了写响应通道。

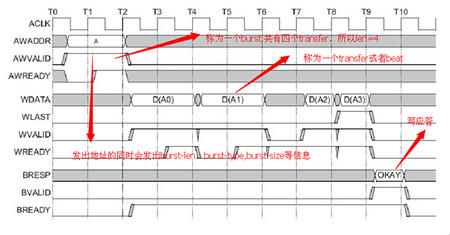

2、AXI传输首先发出burst的长度(burst-len),最大是16,burst长度就代表有多少个transfer或者beat,一个transfer就代表一个数据位宽的数据,所以一个burst最大的传输数据长度为burst_len*transfer_width;在发出burst长度时会同时发出当前这个burst中第一个transfer的首地址,后面其它的transfer不会有地址,slave要根据地址递增的方式自己去进行相应的处理,这个地址可以是非对齐的;在发出burst长度时会同时发出burst_size,这个size代表当前burst中所有transfer中最大的字节个数,在发出burst长度时会同时发出地址递增方式burst-type,是不变地址(non-incr),是递增(incr)还是wrap,例如:当前要传输11个字节,地址是2,数据位宽是4B,所以传输方式是:2B-4B-4B-1B,burst_len=4,burst_size=4(所有transfer中size最大的),地址是2(因为支持非对齐传输),burst-type=incr;对于写会有strobe代表当前transfer中哪几个字节是有效的,所以上面的strobe为:1100-1111-1111-0001,对于读则没有,但是Master自己清楚哪些数据是有效的,所以可以将整个4B都读出来,master自己去除无用的数据。

注意:不同人对burst_size(也就是英文手册中AWsize和ARsize的理解)的理解可能不同,手册中在table-4-2中有解释,它表示一个burst中transfer中max-num,注意最大,所以不是表示当前burst中所有transfer的num,只是表示最大。如果表示所有transfer的num,那么也就是所有transfer的大小是一样的(AHB就是这样的,每个burst中的transfersize是一样的),那么上面的例子就必须分成3个burst,第一个burst,len=1,size=2,addr=2, 第二个burst,len=2,size=4,addr=4, 第三个burst,len=1,size=1,addr=12,显然这个效率要比上面的低。不过呢,如果你的设计中大家都约定成统一的理解倒也可以实现,只是你的AXI就不是通用的AXI,别人不能用。

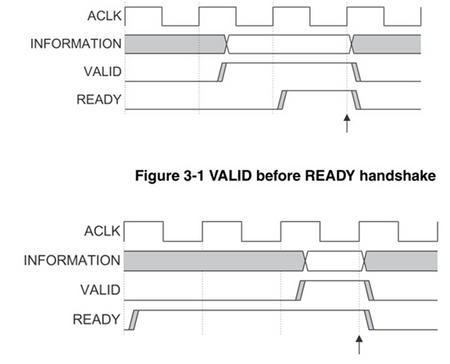

3、AXI中关于valid和ready的关系在3.3节中有很好的解释,在设计时一定不能设计一方依赖另一方,否则会出现死锁的现象,valid可以优先于ready拉高,也可以在ready之后拉高,它们并无先后关系,其实只要是master准备好就可以valid,slave准备好就可以ready,并无绝对的先后顺序,但是当两者同时为高则表示当前的data或者cmd结束或者开始下一个data或者cmd。

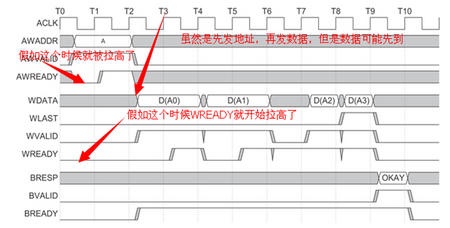

4、由于3中的不确定性会出现一种奇葩的现象,以写为例,会出现写数据比写地址先到达slave的现象,原因如下:假如AWREADY和WREADY被slave提前拉高了,虽然master那边肯定是先发地址再发数据,但是master会误以为slave能够立即接收地址,所以地址发送完立即发送数据,但是地址通道和数据通道是分开的,axi允许单独对各个通道进行优化,所以,如果地址通道被插入了多个reg,那么就会造成延时,可能出现数据先被slave收到。

|

|