|

- UID

- 1062083

- 性别

- 男

|

本文以X射线透射衰减规律为基础,提出了一种基于DSP的X射线能谱数据采集系统的设计方案。本方案重点介绍了用于能谱数据采集的硬件电路和软件设计,其中,硬件电路主要由前置放大、滤波、主放大、峰值保持电路组成,软件主要由 TMS320F2812对经过预处理后的脉冲信号进行多道脉冲幅度分析操作,并最终绘制出X射线能谱图。经调试结果表明本系统具有电路设计简单,采样精度高,抗干扰能力强等特点。

0 引言

X 射线是由高能电子在物质中作减速运动或由原子内层轨道电子的跃迁产生的,所以穿透性很强,广泛应用于射线检测、介质识别等多个方面。在射线能量一定时,X 射线辐射强度的衰减程度只与所穿过的介质有关,即X射线穿透不同介质时,透射的强度不同。所以,可以通过对探测到的X 射线强度分析从而进行介质设别的相关研究。

X 射线的探测是通过探测器接收到射线穿透物质后射线的强度来实现的,本文采用NaI(Tl)晶体与光电倍增管组成的闪烁探测器以用于X射线的探测,探测器输出的脉冲信号幅度与透射的射线强度成正比,所以对脉冲信号幅度的分析也就为介质识别提供了重要的信息,本文选用高速DSP 芯片TMS320F2812 作为主控制器来完成脉冲信号幅度的分析与处理。

1 系统总体框架设计

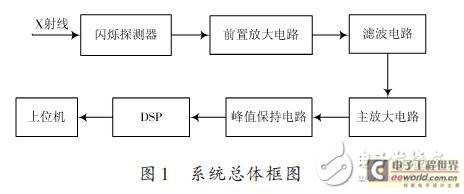

闪烁探测器探测到的X射线强度一般比较微弱,需要经过放大、滤波、峰值保持等预处理后,再使用 DSP对处理后的信号进行A/D 转换、脉冲幅度分析、数据的存储以及与上位机之间的通信,最终绘制出一条有关X射线强度的谱线图。X射线能谱数据采集系统主要由5部分构成:前置放大电路、滤波电路、主放大电路、峰值保持电路、DSP主控电路,其总体框图如图1所示。

2 系统各组成部分的设计

2.1 前置放大电路的设计

前置放大电路是整个前级预处理电路设计的关键,在未屏蔽的条件下,透射的X射线一般处在变压器电磁辐射、工频干扰、背景辐射等背景噪声中,要想从强大的背景噪声中提取出携带识别介质信息的X射线强度,就需要整个X射线能谱数据采集系统具有很高的性能,而前置放大电路又是前级预处理电路前端重要的组成部分,所以本系统所设计的前置放大电路如图2所示。差分运算放大器具有很高的共模抑制比,可抑制各种共模干扰引入的误差。

图2所设计的电路由3个基本运算放大器组成,其中运放A1、A2组成同相并联输入第一级放大,以提高放大器的输入阻抗和增益,A3为差动放大,作为放大器的第二级。整个电路的共模抑制比取决于第一级放大电路中A1 和A2 的对称程度,第二级放大电路的共模抑制比取决于差动运放A3 的闭环增益以及电阻的匹配精度。由图2 可算出前置放大电路的输出电压为Uo当Ui1=Ui2 时,R2 中电流为零,故输出电压Uo=0.可见,电路放大差模信号,抑制共模信号。

2.2 滤波电路的设计

由于噪声与信号同时放大,不利于后续放大电路的工作,所以信号在经过前置放大电路放大后需要进行滤波。为了保证X射线探测的精确性,可在前置放大电路之后设计由压控电压源二阶高通滤波和二阶低通滤波电路串联组成的带通滤波电路如图3所示。

图3即是所设计的带通滤波电路,它由有源高通和有源低通滤波串联组成,其带宽范围为100 kHz~1 MHz.高通和低通滤波的运算放大器选用具有高精度、低偏置、低功耗的双运放芯片LM358.根据有源滤波电路的快速设计理论,可得到高低通滤波器的各个参数。

高通滤波器的带内增益为1,截止频率为100 kHz,高通滤波器的各个参数为:C1=C2=800 pF,R1=R2=20 kΩ;低通滤波器的带内增益为1,截止频率为1 MHz,低通滤波器的各个参数为:C3=C4=1 nF,R3=R4=160 Ω。

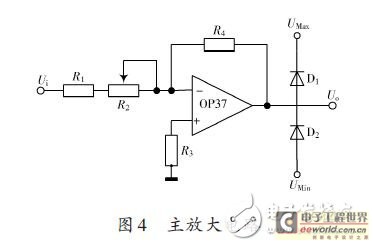

2.3 主放大电路的设计

经过前置放大和带通滤波处理后的信号仍然比较微弱,其中最大的脉冲幅度约为400 mV且为负脉冲,由于后续ADC 电路的输入范围为0~3.3 V,因此脉冲信号在送入ADC 电路之前还需进一步放大,所设计的主放大电路如图4所示。

由图4所示,主放大电路采用具有低噪声、宽带宽、高精度的单运放芯片OP37组成电压并联负反馈电路,为使后端A/D转换电路具有较为理想的输入信号,主放大电路的电压放大倍数设计为6~8 倍,因此图中各个电阻的参数设计为:R1=25 kΩ,R3=30 kΩ,R4=200 kΩ,R2采用标称阻值为10 kΩ的可调电位器。此外,为了避免电路中的毛刺使放大电路的输出超过ADC的输入电压范围,在主放大电路的输出端设计了双向限幅电路,当主放大电路的输出高于UMax 时,二极管D1 导通,此时输出电压被限制在UMax;当主放大电路的输出低于UMin时,二极管D2 导通;选择合适的UMax 和UMin,可以把输出电压钳制在0~3.3 V,满足A/D转换电路输入电压的范围要求。

2.4 峰值保持电路的设计

经过主放大电路处理后的脉冲信号虽然幅度较为理想,但脉冲宽度仍然较小,最小脉宽只有1 ms.而A/D转换需要一定的时间,要采到脉冲的尖峰需要对峰值电压进行保持,同时向DSP 提出中断请求信号,使DSP响应中断并启动A/D转换,转换结束后DSP使采样保持器复原为采样状态,实现系统的逻辑控制,本文设计的峰值保持电路如图5 所示。

如图5所示,U4是芯片LF398,它是美国半导体公司研制的集成采样保持器。它只需外接一个保持电容就能完成采样保持功能,其采样保持控制端可直接接于TTL,CMOS 逻辑电平。U1 和U2 是高速电压比较器LM311,U3 是上升沿触发的双D 触发器,U5 是与门74LS08.经过主放大电路处理后的脉冲信号一路输入到阈值比较器U1,另一路输入到由比较器U2 组成的峰值检测电路(R3C1组成延迟电路与U2反向输入端输入的脉冲信号进行比较,用于判断脉冲信号的峰值是否到来),还有一路输入到采样保持器 LF398,而且LF398的输出接到DSP内ADC模块的ADCINA0引脚上。

当电压脉冲信号幅度大于阈值电压Vref(调试过程中设定Vref 为0.5 V,电压低于0.5 V 的即可认为是噪声而不予考虑),比较器U1输出高电平,产生上升沿,上升沿再触发U3A,它的Q 端输出高电平和峰值未来到时U3B的Qˉ 端相与得高电平,去控制LF398的采样控制端进入采样状态。当脉冲信号到达峰值后,比较器U2 输出高电平,得到上升沿,上升沿再触发U3B,它的Qˉ 端输出低电平,U5输出低电平,LF398进入保持状态。U3B的Qˉ 端输出的下降沿作为DSP 捕获单元CAP3 中断的启动信号,CAP3 发出信号去启动ADC,当A/D 转换结束后,DSP 的GPIO 口输出一个低电平作为U3 的清零信号CLR,双D 触发器74LS74 清零后,LF398 的采样控制端重新进入采样状态,准备保持下一个脉冲的峰值。

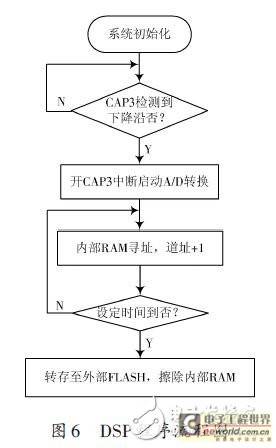

2.5 DSP程序流程的设计

A/D转换和脉冲幅度分析的控制是整个X射线能谱数据采集系统的核心部分,决定着能谱数据采集的精度和整套系统的性能。由于NaI探测器探测到X射线的脉冲宽度最小只有1 ms,一般单片机的指令周期为微秒级,所以无法满足应用的需求。本文设计中选用了高速DSP芯片TMS320F2812,其时钟频率高达150 MHz,时钟周期为6.67 ns,使得A/D转换、对转换结果按幅度分类、进行计数等一系列操作能够在一个脉冲宽度的时间内完成;而且片内自带ADC模块是一个12位分辨率、具有流水线结构的模/数转换器,共有16个采样通道,最高采样频率为12.5 MSPS;该芯片最多可支持96个内部的外设中断,其中一个中断可用于启动A/D转换。

如图5所示,当采样保持器LF398由采样状态进入保持状态时,上升沿触发器U3B的Qˉ 端输出由高电平变为低电平,从而产生下降沿。当DSP事件管理器EV捕获单元CAP3 捕获到这个下降沿时,发出一个信号去启动ADC 并进入A/D 中断,此时高速的A/D 转换器开始将采样保持器LF398 保持的直流电平转换为12位的数字信号,转换的结果保存在ADC 模块的结果寄存器中;同时,DSP 会根据此结果进行内部RAM 寻址,并且对相应的道址进行加1操作,随后DSP通过通用输入/输出多路复用器GPIO产生一路低电平信号,此低电平信号输入到U3的清零端,从而使 LF398再次进入采样状态。在DSP 程序设计过程中预先设定好一定能谱数据采集的时间,等到规定的时间时,DSP将此次采集的能谱数据转存至外部Flash 存储器,并且清除存储在内部RAM 的能谱数据,以便进行下一次的采集,本文DSP处理的软件流程如图6所示。

3 系统调试结果

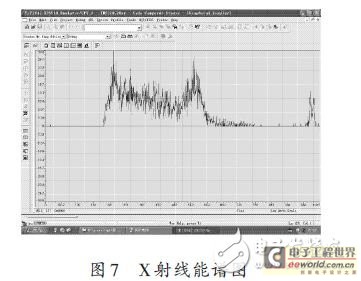

当X 射线能谱数据采集系统各部分硬件电路调试成功时,就需要配合NaI(Tl)探测器进行系统联调。X 射线发生装置通过给X光管加80 kV的高压使之产生X射线,NaI(Tl)探测器探测到X射线后通过内部的光电倍增管产生电压脉冲信号,此脉冲信号经过系统各部分硬件电路逐步处理后,再通过TMS320F2812 的串行通信接口SCI上传到计算机分析处理,并最终绘制出X射线能谱图。系统结果的调试是在TI公司的集成开发环境CCS3.3中完成的,调用 CCS3.3的图形显示窗口,绘制的能谱如图7所示。

由图7 可知,本文的道址数设定为1 024,由于TMS320F2812 的ADC 是12 位,因此需要将A/D 转换后的数据进行寄存器右移2位操作。整 |

|