基于Visual DSP++4.0开发的TigerSHARC DSP多处理器系统及其应用 (3)

|

- UID

- 1029342

- 性别

- 男

|

基于Visual DSP++4.0开发的TigerSHARC DSP多处理器系统及其应用 (3)

向一个激活的TCB写数据时,如在完成当前传输之前,那么,使用相同的DMA通道执行数据的回写操作,可能会导致非法操作,其错误标志将保存到DMA状态寄存器(DSTAT)中。

2.3 ID1到SDRAM的DMA传输

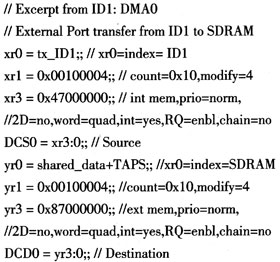

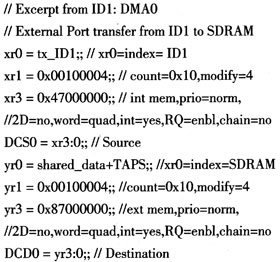

下面的实例是从内部存储器到SDRAM的DMA数据传输(只是从ID1,而不是ID0)。可应用相同的概念设置源和目的TCB:

本例中,源TCB中装入的值和前面(xR3:0)寄存器中的值相同,唯一的差别就是索引量现在指向ID1的内部存储器tx_ID1。目的TCB中写入的值与yr3:0寄存器的值相同,而此处yr0指向shared_data+TAPS。TAPS是指到缓冲区后半部分的偏移量,该缓冲区可在SDRAM中防止覆盖ID0已经传输的数据,以便下一次使用通道0。

2.4 从ID1到ID0的核传输

核传输是不使用DMA的另外一种数据处理方式。这种情况下,整数算术逻辑单元(IALU)用于从ID1到ID0内部存储器的数据传输。实例说明如下:

本例说明了两个数组,每个DSP的内部存储器中都有一个。通过MMS(tx_ID1到tx_ID0)可用ID1将数据写到ID0中的数组中。IALU寄存器用于访问两个数据缓冲区,以执行直接数据传输。

3 ID检测

在多处理器系统构建完成后,接下来还要注意:所生成的可执行文件要载人到该系统中正确的DSP中,以免出错,以下子程序可用于检测所生成的可执行文件是否载入到了系统中正确的DSP中,以确保没有ID失配:

该程序可从SYSTAT寄存器中读入DSP的ID值,并和DSP的理论ID值相比较。本例中的程序为ID1编写,因此,应保证它载入到了正确的目标DSP1。如果不正确,程序就会进入无穷循环,同时标志错误发生。

4结束语

除了多处理器系统的构建方法和数据传输的模式外,MP系统应用中还有DSP资源的分配、总线连接和多DSP系统与FPGA等内容。随着ADSP-TS201S芯片的广泛应用,该处理器的运算速度、存储能力和通信逻辑处理优势已明显的表现出来,而且链路口的传输速度、可靠性和灵活性也较以前有了较大的改观。TigerSHARC功能强大的运算单元和支持多处理器并行处理的特性,使得它特别适用于复杂的系统,如国防工业、医用图像处理以及复杂无线通信算法的处理。 |

|

|

|

|

|