|

- UID

- 1029342

- 性别

- 男

|

本 文所用的SoC测试案例由硬盘控制器(HDC)、16位微控制器、微控制器使用的程序和数据SRAM以及用8M位DRAM实现的片上缓存组成,再加上时钟 综合PLL、带外部旁路晶体管的稳压器使用的片上控制电路组成一个完整的系统。该器件采用的是0.18μm的铜工艺,与前几代技术相比增加了性能、降低了 功耗。另外,DRAM也采用了深亚微米技术,因此在一个器件中可以包含进一个完整的系统缓存(1MB)以及自动刷新逻辑,而且使用的硅片面积还比以前小。

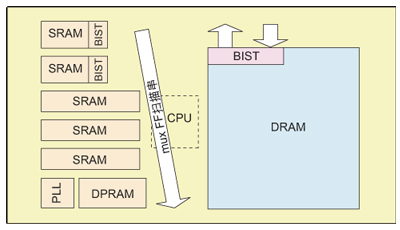

| 图1:扫描模式配置。

|

本 文还讨论了DFT和DFM所采取的对策,包括为了实现更快的良品率学习曲线而采用面向分析工具的设计、为减少测试成本而采取的并行测试方法。DFT和分析 存取是通过IEEE 1149.1的JTAG控制器实现的。除了专门的存储器测试和ATPG扫描外,JTAG控制器还能为组成完整SoC的各个不同单元提供各种测试模式配置。 所采用的设计对策决不是只有唯一一种可能性。由于存储器在器件中占了45%的硅片面积和86%的晶体管数量,因此需要对存储器加以重点关注。存储器测试是 重点考虑和努力开发的对象。

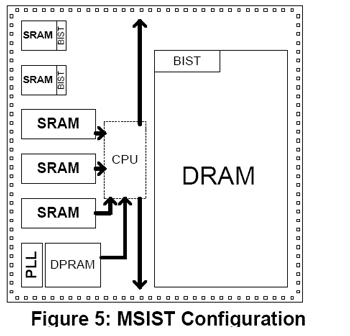

SRAM有两种测试方法,具体取决于SRAM在系统中的用途:CPU存储器(代码和数据)是通过 微控制器进行测试的,需要特殊硬件配置和测试模式的支持;与HDC相关的SRAM采用存储器BIST电路进行测试。DRAM则通过BIST控制器进行测 试,而DRAM BIST自身利用扫描和ATPG进行测试。大多数数字逻辑是完全综合过的,而所有数字逻辑都要经过ATPG扫描测试。另外,象PLL和稳压器控制等模拟电 路则采用特殊编制的程序在特殊测试模式下进行测试。本文首先介绍系统级芯片本身,包括SRAM和嵌入式DRAM,然后简要讨论用于指导DFT和DFM开发工作的分析与生产测试对象,最后阐述了SoC中采取的分析和生产测试对策。

系统级芯片概要

为 了有助于了解生产测试与分析所采取的对策,首先让我们看一下SoC的一些细节,当然本文提到的所有性能都需要进行测试。这款SoC的主要系统组件有:16 位微控制器、ASIC逻辑(硬盘控制器或HDC)、微控制器使用的SRAM、片上缓冲DRAM、时钟综合PLL、硅工艺-电压-温度(PVT)传感器以及 带外部旁路晶体管的稳压器用的片上控制电路。

1.微控制器

这款SoC中的微控制器是C173系列处理 器的衍生产品,是专门为控制应用设计的16位器件。除了16位的C163内核外,它还有一个乘法累加单元(MAC)、外围通用定时器(GPT)、异步和同 步串行控制器(ASC,SSC)和脉宽调制器(PWM)。整个微控制器是由综合过的逻辑实现的,可以很方便地在应用之间移植。

2.ASIC

硬 盘控制器(HDC)是用大约25万个NAND等效逻辑门实现的。该HDC的主要特点之一是能够提供功能强大的节电模式。微控制器、HDC部件、存储器和 PLL等各自所实现的节电模式是不同的。微控制器可以被切换到空闲或睡眠模式。在空闲模式下控制器内核停止工作,但通用定时器和PEC控制器等外围设备仍 在正常运转。只有进入睡眠模式后外围设备才被切断电源,此时只有中断控制器能唤醒微控制器,并使其返回到正常的工作模式,中间过程不会丢失任何数据。中断 控制器是由相应的硬件信号驱动的。

针对HDC的操作特殊性,HDC还提供另外一种电源关闭模式。每个模块的电源都可以被独立 关断,或者时钟系统速度可以降低8倍。这些节电模式的灵活组合就形成了活动、空闲模式1、空闲模式2、等待、睡眠等各种符合ATA规范的节电模式。通过这 些措施可以使SoC的功耗从270mW降到54mW。

| 图2:MSIST配置。

|

3. CPU SRAM

上述这款SoC集成了80KB的程序SRAM、8KB的数据SRAM以及直接与微控制器相连的2KB双端口SRAM。

4. 缓存DRAM

一 个完整系统的集成中心是嵌入式DRAM,在本例中即是1MB或8Mb的片上存储器。DRAM可以在没有离开芯片的总线条件下提供程序和数据存储,所有这些 的功耗在全负荷情况下也只有0.1瓦。内部256位的数据总线宽度允许全速访问DRAM,而片上缓存还可以优化CPU对程序存储器的访问。DRAM本身在 发生页面改变这种最坏情况下(随机存取)的存取时间是20ns,在页面突发时的存取时间是7ns。

5. 系统单元:PLL、PVT、稳压器

PLL 所需频率的时钟产生都是靠片上的500MHz PLL实现的。这个PLL是一个全定制的宏,由JTAG控制器控制其测试模式。工艺-电压-温度(PVT)单元用于向SoC报告环境状况。SoC负责通过 一个标准的ATA接口建立与主计算机之间的通信。为了充分满足信号完整性要求,系统必须对各种操作状态作出反应,如电缆和主机接口特性等静态环境条件、不 稳定的温度和电压等动态变化等。另外,给定器件的工艺参数会在制造用的工艺窗口范围内变化。SoC包含PVT单元就是为了及时对这些因素作出响应。PVT 单元能够监视动态/变化中的环境,HDC中的相关逻辑可以自动调整ATA衬垫处的性能参数。PVT单元是一个全定制宏,这个单元的测试模式受JTAG控制 器的控制。 |

|