本帖最后由 yuchengze 于 2016-12-27 13:05 编辑

很久以前人们便预测,未来的设计与测试会相互结合--在完整的系统设计流程中,这两种一向井水不犯河水的功能会整合在一起。只要纳入符合设计的测试定义与操作,整合两者的好处可说是显而易见,不仅能缩短上市时间,还可以提高整体品质。这些测试台可于系统设计流程中重复使用,因其包含模拟、操作,以至于最终系统部署等步骤。为整合设计与测试,尤其是针对射频(RF)通信等较为复杂的功能,系统设计软件与所选语言必须能同时针对测试与操作,在整个设计周期中有效运作。

一般而言,用于模拟/设计系统的工具与技术不同于运用在操作系统的工具与技术。此外,设计/操作专用的工具和语言也不同于测试工具和语言。这样一来,便需要不同的团队,各有各的职责与工具,所以不仅会提高沟通的难度,也会因此降低设计与测试中重复使用程序码的流畅度。

以上这些情况都会有损设计/测试相互整合的好处,因此理想的系统设计软件一定要提供可同时用于模拟、操作、测试的单一语言,并且尽量重复使用所有的设计函式与相位。

传统做法枝节横生

一般来说,如果特定工具能同时用于设计流程的各种相位与函式,是因为这种工具会尽量减少每个相位与函式间的阻碍,而非建立通用的环境和语言。例如,在新兴RF通信标准的开发流程中,通信系统设计专家可能会仅以运算式与数学的角度出发,进而制作模型并模拟通信串流。

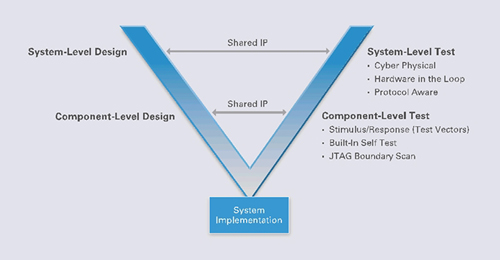

如要测试此模型,设计人员可能会建置自己的测试台,但假若是针对业界标准的通信协定,就可能会重复使用合格的测试台。一旦能符合设计函式,设计就算告一个段落,操作团队会接手运算式,并且动手将数学运算式编译成操作运算式,这时通常会根据相关的执行需求来决定该使用ANSI C或硬体描述语言(HDL)(图1)。

图1 「V」程序图通常用来代表理想的设计、操作、测试流程。在整个「V」程序图中一律使用某种系统设计语言,这样做不仅能有效重复运用相关知识和运算式,也可以减少编译错误,同时缩短发现错误并加以修正的时间。

此外,测试台本身也须要经过编译。这项工作需要另一个不同职能的团队负责,而且编译过程中如果出现任何遗漏,经常会造成新的错误,也可能会缩小测试范围。如果初始编译层不够复杂,就必须从头设计或什至会发现其他操作错误,让整个情况雪上加霜。设计运算式无法衔接操作流程,会进一步延缓发现错误并加以修正的时程。

为缓和这类问题,许多工具都加入自动产生程序码的步骤,进而提高模拟程序码编译成ANSI C或HDL的速度。虽然这么做有助于加速迁移至处理器或现场可编程闸阵列(FPGA),却无法避免系统部署与除错等需求,这必须交由熟悉ANSI C或HDL的人员负责;即便原始设计并不完美,但自动产生的程序码可能也有某种缺陷。

图形化软件提供单一工具方法

市面上有众多的系统软件,以产品时程的观点来看,图形化软件所提供的成效可以大幅协助工程师缩短测试时间,以美商国家仪器(NI)LabVIEW系统设计软件为例,此软件提供全然不同的选择,通信设计人员可在制作通信串流模型与直接操作测试台时一并使用。如果系统设计人员对设计与测试成果感到满意,即可将设计运算式直接用于处理器或FPGA以便进行操作。

从早期探索性质的设计阶段开始,一直到最终的操作阶段,系统设计人员都能使用相同的环境、运算式、除错与测试方法。这样一来,即可有效重复使用相关知识和运算式,也可以减少编译错误,同时缩短发现错误并加以修正的时间。

至于纯函式的数字信号处理(DSP)类型运算式,系统设计人员可以超高速度操作运算式并加以除错,这是连续时域模拟方式所望尘莫及的。至于针对FPGA的设计模拟,还能进一步突显这项好处。

提供RF通信设计测试弹性

针对RF应用整合设计与测试的议题,通信设计也为这种趋势带来某种程度的复杂问题。最重要的是,若要测试RF接收器,必须先建置传输器,如果想测试传输器,又得先建置接收器。

一般来说,这些测试器的信号与测量特性必须胜过设计本身的相关特性。此外,RF通信方法与标准日新月异,因此测试器的弹性与速度也必须与时俱进。所以就RF领域而言,理想的测试仪器必须能快速重复使用传输/接收DSP表达式,同时具有最优异的性能与弹性。 |