Virtex-Ⅱ Pro FPGA的嵌入系统设计与应用

|

- UID

- 1029342

- 性别

- 男

|

Virtex-Ⅱ Pro FPGA的嵌入系统设计与应用

随着通信技术的飞速发展,为满足高速数字电路和数字信号处理等对时钟管理、信号完整性、高速宽带接口的要求,高速处理器与通信的融合日趋紧密,高速处理器、可编程逻辑器件和高速存储器成为设计的关键。Virtex- ⅡPro 系列FPGA 将可编程逻辑结构和高速处理器集成在同一芯片内部,直接的连接克服了利用总线在FPGA 和附加外部处理器之间接口的瓶颈。

Virtex-II Pro 简介

Virtex- ⅡPro 系列最大容量的FPGA 目前能提供多达5 万个逻辑单元具有超过10 Mb 的RAM;556 个乘法单元12 个数字时钟管理单元以及24个集成3. 125 GbPs 的Rocket IOTM 收发器最大可提供1 200 个IO 引脚, 支持CMOS、SSTL 、HSTL 、LVDS、GTL 和3. 3V PCI 信号标准。Virtex - II Pro 系列FPGA 支持多达4 个运行频率高达300 MHz 的PowerPC 405 处理器。PowerPC405 采用嵌入式300 MHz哈佛(Harvard) 结构的RISC 核具有五级数据通道流水线、硬件乘除单元、32 个32 位通用寄存器、16 KB指令Cache 和16 KB 数据Cache 、1 KB~16MB 可变页尺寸组成存储器管理单元(MMU) 和专用的片内存储器接口。

PowerPC405 处理器由IBM CoreConnect 技术支持,CoreConnect 是运行在100~133 MHz 的64 位总线,为了使系统设计灵活性达到最大,CoreConnect 结构是作为软IP 核在Virtex - ⅡPRO FPGA 中实现的。CoreConnect 总线结构有2 个主要总线组成,处理器局部总线(PLB) 和片内外设总线(OPB) 。这些总线可以用来分别连接高速和低速外设到PowerPC处理器。此外,设备控制寄存器总线对通用外设器件寄存器的进行管理和控制。

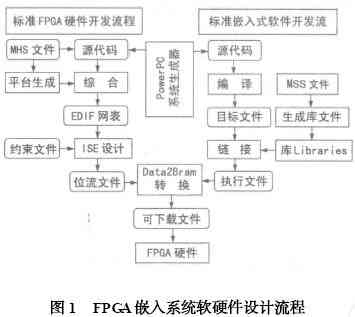

EDK(Embedded Development Kit) 是Xilinx 公司提供的嵌入开发工具,用于在FPGA 内部集成多种不同的IP 核,可方便地规划、设计并生成整个片上系统的硬件和软件结构。通过编写硬件描述文件(MHS) 来设置FPGA 内部硬件系统,主要包括定制嵌入处理器PowerPC405、外围设备IP 核、设定外部存储器和其他外设的地址空间、管理外围设备的控制信号及中断信号。EDK 的硬件生成平台根据用户编辑的MHS 文件生成相应的VHD 文件,原理图文件等,同时支持系统仿真。EDK工具提供了大量可供使用的IP 核, 包括SDRAM,DDRRAM,UARTController ,10/ 100 M以太网MAC ,总线仲裁器等,使FPGA 可方便地与其他外围器件连接。EDK 实现FPGA 片内软、硬件设计过程如图1 所示。

应用系统结构

数据纠错译码接入设备要求对同步传输的数据进行帧同步、解扰、纠错译码处理并对处理后的数据进行网络接入。在以太网接入部分,要求对解码后的数据进行IP 协议封装,然后使用数据链路层协议对协议包进行以太网帧的封装,最终通过网口接入局域网。

在对Virtex - II 系列FPGA 充分理解和研究的基础上,根据系统设计需求,进行系统硬件的设计。本设计采用了VII - Pro 系列的XC2VP7FG456 芯片,在芯片内部设计嵌入了一个PowerPC405 处理器IP核。应用系统由XC2VP7FG456 芯片及其上电复位电路, 系统时钟电路、内存电路、程序存储电路、PROM电路、以太网PHY接口电路和RS - 232 接口电路、JTAG接口、LVPECL 电平接口电路组成。系统组成框图如图2 所示。 |

|

|

|

|

|