|

- UID

- 871057

- 性别

- 男

|

摘要:恒虚警在着陆雷达系统中有着重要的作用和地位。恒虚警处理可以避免杂波变化影响检测阈值,提高雷达在各种干扰情况下的检测能力。文章首先介绍了恒虚警检测的原理,然后对几种典型方法进行了比较,选定单元平均选大恒虚警检测方法进行设计,并且实现了基于ADS P-TS201的恒虚警处理,最后通过Visual DSP++进行了仿真验证。

关键词:着陆雷达;恒虚警;ADSP-TS201;单元平均选大恒虚警

精密进场雷达以飞机作为主要探测目标,地物、云雨雪等都被视为杂波干扰,所以在设计中总是尽可能地采取措施抑制干扰,提高雷达发现目标的能力。为了使设备正常工作,干扰电平允许变化范围通常比较小。雷达内部的热噪声、地物、气象杂波的干扰电平很大,其变化有时高达几十分贝。为了设备能稳定正常的工作,必须保持虚警概率基本不变,因此,信号处理分机增加了恒虚警(CFAR)处理电路。

近年来,CFAR方法出现了很多,然而,真正应用的并不多。通过对4种具有代表性方法的比较,得到一种可以实现且检测性能较好的恒虚警处理方法。

1 恒虚警检测方法

恒虚警检测方法就是采用自适应门限代替固定门限,而且此适应门限能随着被检测点的背景噪声、杂波和干扰的大小自适应地调整。如果背景噪声、杂波和干扰大,自适应门限就调高;如果背景噪声、杂波和干扰小,自适应门限就调低,以保证虚警概率恒定。所以设计雷达恒虚警检测器的关键是获取这种自适应门限的方法。

常见的恒虚警检测器有4种,单元平均恒虚警(CA-CFAR)检测器提供了对非起伏和斯威林起伏目标的最优或准最优检测,但是,在杂波边缘要引起虚警率的上升,将导致检测性能下降,在杂波边缘的检测性能会明显变坏。平均选小恒虚警检测器(SO-CFAR)是就干扰目标提出的,但也仅在大干扰目标的情况下有效,而当两个相差不大的大干扰出现在检测单元两侧时,性能恶化,所以这种方案的局限性很大。平均选大恒虚警检测器(GO-CFAR)可以明显消除普通单元平均对数恒虚警电路在杂波过渡区内存在的虚警增加的现象。单目标、均匀杂波背景情况下,GO-CFAR是这几种方法中最优的。

2 恒虚警电路设计

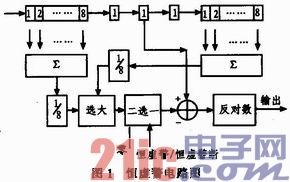

着陆雷达恒虚警电路采用平均选大恒虚警检测方法。恒虚警检测器的参考单元N取16,如图1所示。

设计思路是:将检测点的幅度减去噪声的平均值(由虚警电位器调整),再将相邻七个距离单元的信号进行相关运算,若超出虚警门限,则作为有用目标信号处理,输出高电平,打开实时信号选择支路;若低于虚警门限,则作为虚警信号处理,输出低电平,关闭实时信号选择支路,阻止视频信号输出。图中,被测信号单元两侧各空一个单元,使目标信号本身不参与杂渡均值的估计,这样可以避免被测单元对杂波强度估计值的影响。3 实现电路

ADI公司的ADSP TS201处理器片内集成大容量存储器,兼有ASIC和FPGA的信号处理性能,能够支持本次设计的实现,其实现电路组成如图2所示。

其中先出寄存器模块FIFO1存贮前8个距离单元的回波数据,而先进先出寄存器模块FIFO2存贮后8个距离单元的回波数据之和的平均值。输入数据进入芯片内部,经累加电路(采用加新值,减旧值的方案),前8个距离单元数据之和,在CP4脉冲到来时打入寄存器Rag1中,同时后8个距离单元数据之和的平均值也由FIFO2中取出,并存在寄存器Rag2中,二者经选大后大者存在寄存器Pag5中,同时被测数据也存入寄存器Rag4中,二数据经减法运算,其差送出芯片,再经反对数电路,得到恒虚警输出。

8个距离单元的数据累加器,在零距离的前8个距离单元时间内要完成初始化过程:加新值减去零,这样经过8个距离单元,累加寄存器内将保持着前8个距离单元的数据之和,从第9个距离单元开始,才进行“加新减旧”运算,这样使累加器和寄存器内总是保存当前最新8个距离单元的数据之和。这样,只有经过19个距离单元,后8个距离单元数据之和的平均值才有效。故FPGA内部需产生两个清零信号:FIFO1输出寄存器清零信号为CLR1,FIFO2输出寄存器清零信号为CLR2。雷达的航向天线和下滑天线是以1 Hz的频率交替工作的。当天线转换时,其存贮器内仍保留着另一个天线扫描时的数据,这些数据需要废弃,而要存贮扫描后的新数据,且要不断地更新。当接收到天线转换的信息时,要产生两个清零信号:CLR1和CLR2,分别对两个存贮器清零。

估直流电路是在雷达休止期内,取16个距离单元,电平在恒虚警和非恒虚警两种工作状态时,直流电平基本不变。

4 仿真验证

运用针对ADI公司的DSP器件而专门开发的平台一Visual DSP++进行编程仿真,验证所设计的恒虚警电路功能。输入一组雷达原始数据,对其进行处理,根据输出的波形验证此检测器。输入信号波形如图3所示,输出信号波形如图4所示。

由图3可知,目标信号湮没在各种噪声中,必须经过滤波处理才能得到所需信号波形。将雷达信号数据输入仿真系统,从图4输出信号波形上看,波形较为理想,达到了预期目标。

通过仿真验证,发现输出信号已经将杂波大部分滤除,所得信号基本与所需目标信号一致,结果比较理想,说明设计比较合理。

5 结束语

文中着重介绍了一种着陆雷达恒虚警处理的实现方法,并在FPGA上进行了电路设计,最后通过仿真进行了验证,取得了较好的效果。 |

|