|

- UID

- 871057

- 性别

- 男

|

摘要:OMAP4430是TI公司推出的开放式多媒体可扩展应用平台,对于移动通信开发应用具有一定的价值。本文主要从硬件结构、软件架构两个方面进行阐述,突出OMAP4430的低能耗、高性能、高集成度以及在现代通信与多媒体技术中的相关应用。

关键词:OMAP4430;开放式应用平台;主体结构;软件架构

引言

现今随着多媒体技术以及通信技术的迅速发展,信息通信正悄无声息地改变着人们生活的点点滴滴。TI公司与时俱进地提出了一种解决方案:开放式多媒体应用平台——OMAP。OMAP4430基于OMAP体系,不仅与其他OMAP处理器一样,采用开放式、易于开发的软件设施,支持多种操作系统,而且具有更高的处理能力和更低的功耗。OMAP4430开放式平台主要应用于移动智能手机以及移动互联网设备(MID),它以强大的性能以及可编程性有效地支持了未来移动互联网应用的发展,并且使得下一代移动智能手机和MID被快速推向市场。由此,OMAP4430必将在通信,特别是移动通信中发挥关键的作用,也必将越来越广泛地应用于通信领域中。

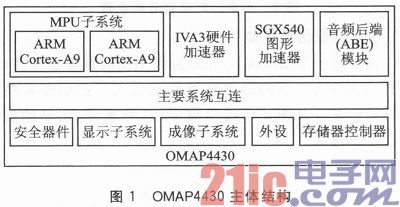

1 OMAP4430主体结构

OMAP4430高性能应用平台基于OMAP体系,并且采用45 nm技术,被设计用来为各种应用提供一流的视频、图像、图形处理技术,主要支持以下几个功能:每秒30帧1920×1080P的全高清(HD)视频流媒体、平面(2D)/三维(3D)的移动游戏、视频会议以及最大可以支持1600万像素的高解析度静止图像。由图1可以看出,OMAP4430主体结构主要由微处理器单元(MPU)子系统、IVA 3硬件加速器、SGX540图形加速器、成像子系统、显示子系统以及音频后端(ABE)模块等组成。

1.1 MPU子系统

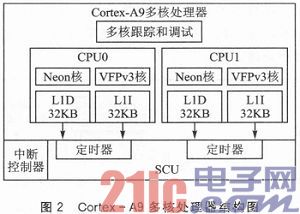

OMAP4430的MPU子系统采用双核架构,由两个ARM Cortex—A9 MPCore处理器组成。ARM Cortex—A9 MPCore处理器与其他Cortex系列处理器以及ARMMPCore技术兼容,因此能够沿用包括操作系统/实时操作系统、中间件及应用在内的丰富生态环境,从而减少采用全新处理器所需的成本。Cortex-A9处理器支持对称多处理(Symmerical Multi—Processing,SMP),SMP允许相同的处理子系统运行相同的指令集,平等地访问内存、I/O接口和外部中断,以及运行一个操作系统的副本来控制所有核心。Cortex—A9处理器具有很高的运算速度,性能是ARM Cort ex—A8的1.5倍,且主频达到1 GHz,能在每个循环中执行多达4条指令,同时还能减少目前主流8级处理器的成本并提高效率。

双核Cortex—A9 MPU子系统中的两个Cortex—A9中央处理单元(CPU)之间共享2级(L2)高速缓存,并且使用PL310作为L2高速缓存控制器。每个CPU都有32KB的1级(L1)指令高速缓存、32 KB的L1数据高速缓存、独立的专用电源网域以及包括NERO技术和向量浮点单元(VFPv3)的协处理器。双核Cortex-A9 MPU子系统还包括标准的CoreSight片上调试和跟踪器件,用以支持SMP的调试和仿真、探听控制单元(SCU)、中断控制器(GIC)以及时钟和复位管理器。

MPU子系统Cortex—A9多核处理器具体结构如图2所示。

1.2 IVA 3多媒体加速器

IVA 3多媒体加速器主要分为两部分:功耗优化、多标准的主流编码器及基于新兴编码器和音频的可编程数字信号处理器(DSP)。这里的DSP为TI公司的C64xDSP,内有2个数据通道、8个功能单元和2个一般目的寄存器文件,采用超长指令字(VLIW),具有双16位扩充功能。

IVA 3支持高达1080P、30帧1 s的2D全高清多标准视频编码/解码和720P的3D高清立体视频编码/解码,它的多标准编码器支持包括H.264HP、MPEG-2MP、MEPG-4ASP、ON2VP7、VC-1AP等在内的主流视频编码,它的可编程DSP可解决未来发展的编解码标准。

IVA 3将使用eXpressDSP数字媒体(xDM)标准为原则的软件界面。xDM标准通过应用程序调用一个特定类别,如视频解码或者音频解码的编解码器来定义应用编程接口(API)。1.3 SGX540图形加速器

SGX540支持2D和3D图形应用程序,是新一代可编程的图形信息处理内核,并支持所有主要的API,包括OpenGL ES2.0、OpenGL ES1.1、OpenVG1.1和EGL1.3等。SGX540的V1.2.0架构是可扩展的,并且可以针对各个细分市场从主流移动设备到高端台式机图形,应用于功能手机、PDA以及掌上游戏应用。

1.4 ISS设计

成像子系统(Imaging Subsystem,ISS)处理来自外部图像传感器的像素数据,数据来自存储器或者在IVA3中的SL2存储器。ISS由3个子部分组成,包括:接口互连部分、图像信号处理器(ISP)以及静止图像协处理器(SIMCOP)。ISS是诸如相机取景器、视频录制、静态图像捕捉等多媒体应用的一个关键组成部分。ISS的设计使大图像传感器实现高吞吐量和低延时,在高性能模式下,ISS支持达到200 Mpix/s的像素吞吐量。ISS与运行实时操作系统的低中断延时微处理器单元Coretex—M3相结合以达到最佳的性能,主要是因为Coretex-M3微处理器单元可以快速改变ISS在帧消隐期问的配置以及运行一些测序任务。

ISS接口部分分为系统接口互连和摄像头接口。系统接口互连包括2个32位宽的配置接口、128位宽的数据接口、本地互连等,一个32位宽的配置接口与Cortex—M3微处理器单元相联系,另一个32位宽的配置接口与Cortex—A9及系统直接访问内存(SDMA)相联系,128位宽的数据接口与3级互连(L3)相联系,本地互连连接ISS内的所有模块。摄像头接口有两个:主级接口和次级接口。主级接口(CSI2-A)支持有4个数据信道的CSI2协议,次级接口(CSI2-B/CCP2)支持一个数据信道的CSI2协议或者CCP2协议,所有的接口都能使用ISP,但是不能并发。当一个接口使用ISP时,另一个必须将数据发给内存,尽管如此,ISP依然可以处理内存到内存的数据,也可以利用时分复用来处理。

ISP是ISS中成像和视频应用的重要组成部分,ISP的多媒体器件包括:视频端口(VP)、码型发生器(PG)、图像管道接口(IPIPEIF)、缩放工具(RSZ)、H3A、图像传感器接口(ISIF)和逻辑缓冲存储器(BL)。ISP还可以支持动态内存到内存的处理、高达200 MHz的像素吞吐量、数

字抗混叠、动态缺陷像素校正、镜头失真校正、边缘增强、噪声滤波、稳定化、自动变焦/自动白平衡/自动曝光以及数码曝光,使得图像处理质量得到提高。

1.5 显示子系统

显示子系统为在液晶显示器(LCD)面板或者电视机上显示一个来自存储器帧缓冲区的视频帧提供逻辑。显示子系统是一个灵活的多管道系统,支持多点触控,为本地或外部显示器提供更多色彩和更丰富的视觉感受等,可以通过电视输出、主级LCD1输出或次级LCD2输出显示不同的图像。

主级LCD1输出可以通过显示串行接口(DSI)或者远程帧缓存接口(RFBI),次级LCD2输出可以通过并行CMOS输出、DSI或者RFBI,电视输出可以通过复合信号或者高清晰多媒体接口(HDMI)。

显示子系统由显示控制器(DISPC)、RFBI、两个DSI协议引擎、NTSC/PAL视频编码器以及HDMI协议引擎组成(具体结构见图3)。DISPC拥有一个直接访问内存引擎、两个LCD输出和一个电视输出,且每一个都配有专用的叠加管理器、一个图形管道、3个视频管道,以及一个回写管道。DISPC可以读取存储在存储器中的已编码像素数据,并且将一个叠加层或者一个管道中的输出写入系统内存中。

RFBI拥有8、9、16位并行接口,可以捕获从DISPC的输出像素并且将数据发给LCD中的远程帧缓存区。两个DSI协议引擎为4数据通道复合输入/输出的DSI1(主级),以及2数据通道复合输入/输出的DSI2(次级),支持视频模式、命令模式以及数据交织和多重显示。

NTSC/PAL视频编码器为在电视机上显示一个来自存储器缓冲区的视频帧提供逻辑,通过外部10位视频数/模转换器输出复合信号。NTSC /PAL视频编码器支持NTSC-J、-M、PAL-B、-D、-G、-H、-I以及PAL-M等复合视频标准。HDMI是一种数字化视频/音频接口技术,是适合影像传输的专用型数字化接口,可同时传送音频和影像信号,最高传输速度为5 Gbps,支持色深模式(1080P为10位、720P为12位),同时无需在信号传送前进行数/模转换。HDMI可搭配宽带数字内容保护HDCP,以防止具有著作权的影音内容遭到未经授权的复制。1.6 ABE模块

ABE模块负责管理发起者(Cortex-A9微处理单元、DSP或者直接访问内存管理器)与外设物理接口(多信道缓冲串行端口、数字微控制器、多信道脉冲密度调制器和多声道音频串行端口)之间的各种音频、语音上行和下行数据流,它从发起者或者外部音频芯片(TWL6040或其他)接收语音音频样本并处理后,将其发送到外设接口或者存储器中。

ABE模块由外设物理接口、音频引擎、本地4级互连、定时器(4个通用定时器和1个监视定时器)、时钟和复位管理器以及电源管理器组成,如图4所示。音频引擎是ABE模块的核心部分,它负责处理实时音频信号并且负责所有的数据传输。本地4级互连与Cortex—A9、DSP以及3级互连相连接,其中Cortex—A9、DSP与本地4级互连直接连接,其他如直接访问内存控制器等发起者,通过3级互连与本地4级互连间接连接。ABE模块具有自己独立的电源网域,并且可以在其他器件处于关闭模式时进行音频处理。

2 OMAP4430软件架构

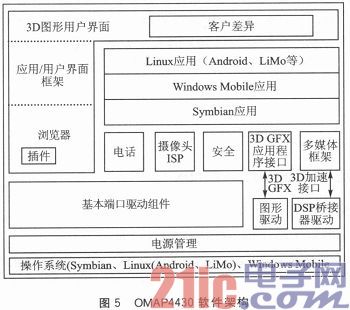

OMAP4430除了有高度集成的硬件结构,还具有完整的软件架构,支持多种主流的嵌入式操作系统、高级语言编程资源和丰富的多媒体组件算法,可通过应用编程接口(API)和第三方开发工具方便地实现各种应用开发,使终端设备制造商和程序开发人员可以更快、更简便地进行开发。此外,软件架构对OMAP4430应用平台的性能和功耗进行优化,以确保产品具有最高的性能。

OMAP4430软件组件,具体框架结构如图5所示,主要包括:移动操作系统驱动程序、板级支持包(BSP)、基使能器、具有多媒体及用户界面/应用框架的预集成硬件加速多媒体编码器、作为具备系统级优化的唯一软件包——预集成连接(GPS、蓝牙、FM、WiFi)解决方案、系统级电源管理、基于集成3D图形及硬件的安全框架、集成的应用套件及跨多个操作系统的用户界面等。除此以外,OMAP4430软件架构还在视频、电源管理、成像、安全、图形用户界面以及互联方面具有与众不同的优势。

2.1 视频软件

为配合IVA 3硬件加速器,TI公司提供了广泛的视频编码,支持每秒30帧1080P的视频,具体格式有MPEG4、ASP、ON2 VP7、H.264 HP、AVS1.0、VC-1 AP、DivX6、Realvideo10以及Sorenson Spark v1等。这些编码支持视频回放、流媒体、摄像机功能、转码、视频电话会议、多路视频回放、多路摄像机、视频推送以及本地记录等使用实例。设备制造商以及开发者可以利用OMAP4430的可编程性解决未来不断发展的视频标准所出现的问题。

响。 |

|