二、定制XILINX CORDIC IP

以ISE10.1软件为例,其集成的CORDIC算法IP为V3.0版本,具体步骤如下:

1.新建工程,点NEW Source…调用IP Core Generator, 输入模块名如MyCordic后按NEXT

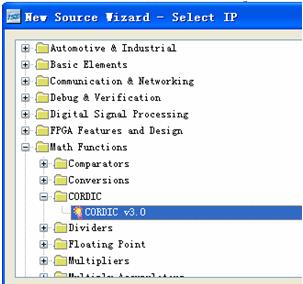

2.在Select IP页面选择CORDIC算法IP,如下图示:

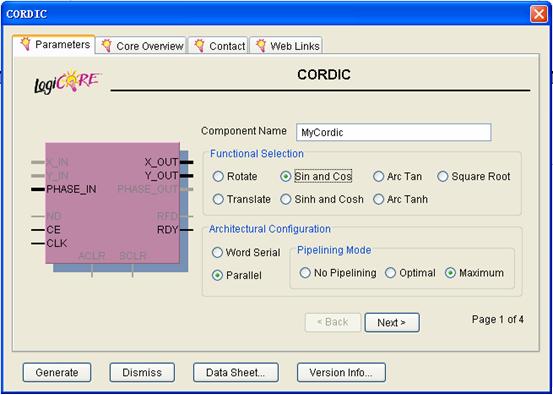

3.点NEXT后进入IP配置界面第一页,如下图示:

这里功能选择处我们选择为Sin and Cos, 其它的为默认就可。

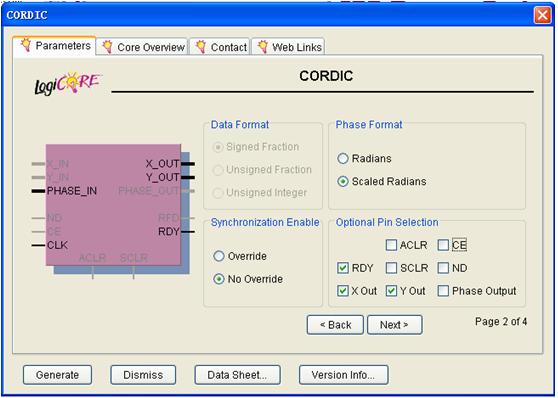

4,点NEXT后进入IP配置界面第二页,如下图示:

这里Phase Format我们选择为Scaled Radians. 并把CE脚去掉。

Phase Format里Radians单位为弧度,Scaled Radians单位为多少PI弧度。

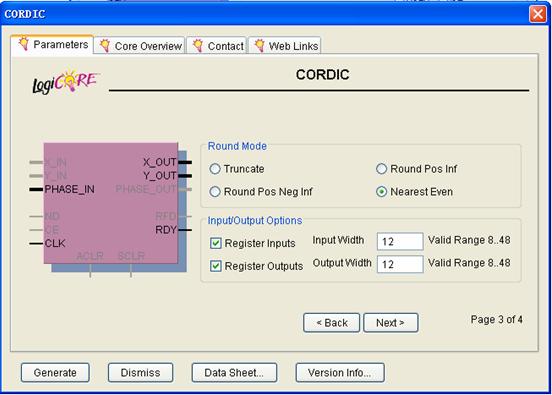

5,点NEXT后进入IP配置界面第三页,如下图示:

根据D/A器件精度,输入输出我们选择12位位宽就可以了,其它的为默认值。

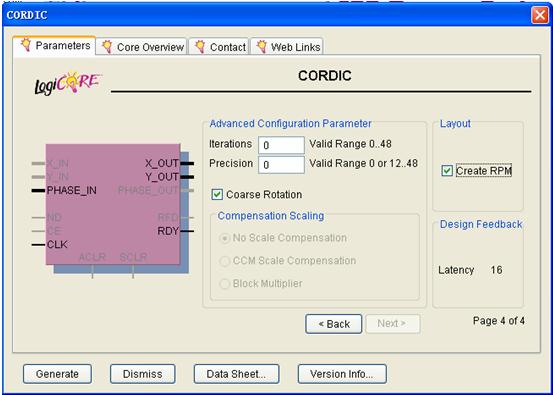

6,点NEXT后进入IP配置界面第四页,如下图示:

在Advanced Configuration Parameters里Iterations指定内部迭代的次数,如果指定为0,则迭代次数会根据所选精度自动选择。Precision指定内部迭代加减时精度,如果指定为0,则迭代精度会根据所选输入和输出的位宽自动选择。

Coarse Rotation用来把相位扩展到整个坐标平面,如果不把它前面的勾选上,输入的相位限制在-PI/4~PI/4,我们在产生正弦波形时必须用到这功能,把它前面的勾选上。

7.最后点左下角的Generate产生IP。说明一下IP引脚功能:

PHASE_IN: 输入的相位。

CLK: 输入时钟

X_OUT: 输出余弦值

Y_OUT: 输出正弦值

RDY: 数据准备好信号,当有新数据时,在第一个时钟周期RDY输出一个高电平脉冲。

8.最后我们需要一个顶层模块来调用CORDIC IP,并通过SPI总线写到赛灵思的Spartan®-3E FPGA Starter Kit开发板板载的DAC器件LTC2624上,我们可以在赛灵思的DEMO s3esk_picoblaze_dac_control基础上修改,把相关代码加到工程,例化一下CORDIC IP,修改Picoblaze程序等等,详细步骤略。

以上抛砖引玉,希望和大家来讨论。 |