|

- UID

- 1029342

- 性别

- 男

|

2. 基于CMSIS标准的软件架构根据调查研究,软件开发已经被嵌入式行业公认为最主要的开发成本。对于ARM公司来说,一个ARM内核往往会授权给多个厂家,生产种类繁多的产品,如果没有一个通用的软件接口标准,那么当开发者在使用不同厂家的芯片时将极大的增加了软件开发成本,因此,ARM与Atmel、IAR、Keil、hami-nary Micro、Micrium、NXP、SEGGER和ST等诸多芯片和软件厂商合作,将所有Cortex芯片厂商产品的软件接口标准化,制定了CMSIS标准。此举意在降低软件开发成本,尤其针对新设备项目开发,或者将已有软件移植到其他芯片厂商提供的基于Cortex处理器的微控制器的情况。有了该标准,芯片厂商就能够将他们的资源专注于产品外设特性的差异化,并且消除对微控制器进行编程时需要维持的不同的、互相不兼容的标准的需求,从而达到降低开发成本的目的。

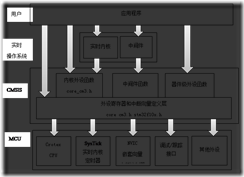

如图 5‑5所示,基于CMSIS标准的软件架构主要分为以下4层:用户应用层、操作系统及中间件接口层、CMSIS层、硬件寄存器层。其中CMSIS层起着承上启下的作用:一方面该层对硬件寄存器层进行统一实现,屏蔽了不同厂商对Cortex-M系列微处理器核内外设寄存器的不同定义;另一方面又向上层的操作系统及中间件接口层和应用层提供接口,简化了应用程序开发难度,使开发人员能够在完全透明的情况下进行应用程序开发。也正是如此,CMSIS层的实现相对复杂。

图 5‑5 CMSIS标准的软件架构

层主要分为以下3 个部分:

(1) 核内外设访问层(CPAL,Core Peripheral Access Layer):该层由ARM 负责实现。包括对寄存器名称、地址的定义,对核寄存器、NVIC、调试子系统的访问接口定义以及对特殊用途寄存器的访问接口(例如:CONTROL,xPSR)定义。由于对特殊寄存器的访问以内联方式定义,所以针对不同的编译器ARM 统一用来屏蔽差异。该层定义的接口函数均是可重入的。

(2) 片上外设访问层(DPAL, Device Peripheral Access Layer):该层由芯片厂商负责实现。该层的实现与CPAL 类似,负责对硬件寄存器地址以及外设访问接口进行定义。该层可调用CPAL 层提供的接口函数同时根据设备特性对异常向量表进行扩展,以处理相应外设的中断请求。

(3) 外设访问函数(AFP, Access Functions for Peripherals):该层也由芯片厂商负责实现,主要是提供访问片上外设的访问函数,这一部分是可选的。

对一个Cortex-M 微控制系统而言,CMSIS 通过以上三个部分实现了:

l 定义了访问外设寄存器和异常向量的通用方法;

l 定义了核内外设的寄存器名称和核异常向量的名称;

l 为RTOS 核定义了与设备独立的接口,包括Debug 通道。

这样芯片厂商就能专注于对其产品的外设特性进行差异化,并且消除他们对微控制器进

行编程时需要维持的不同的、互相不兼容的标准需求,以达到低成本开发的目的。CMSIS中的具体文件结构如表 5‑6所示。

表 5‑6 CMSIS文件夹结构CMSIS

| Core

| Documentation

| CMSIS文档

| CM3

| Startup

| arm

| MDK ARM编译器启动文件

| startup_stm32f10x_hd.s: 大容量产品启动文件

startup_stm32f10x_md.s: 中容量产品启动文件

startup_stm32f10x_ld.s: 小容量产品启动文件

| gcc_ride7

| GCC编译器启动文件

| iar

| IAR编译器启动文件

| TrueSTUDIO

| TrueSTUDIO编译器启动文件

| 本文件夹包含STMF10xxx CMSIS文件:微控制器外设访问层和内核设备访问层:

core_cm3.h:CMSIS的Cortex-M3内核设备访问层头文件

core_cm3.c:CMSIS的Cortex-M3内核设备访问层源文件

stm32f10x.h:CMSIS的Cortex-M3 STM32f10xxx微控制器外设访问层头文件

system_stm32f10x.h:CMSIS的Cortex-M3 STM32f10xxx微控制器外设访问层头文件

system_stm32f10x.c:CMSIS的Cortex-M3 STM32f10xxx微控制器外设访问层源文件

|

|

|