布局布线时间减少近70%---Vivado在复杂FPGA设计中大显身手

|

- UID

- 1023229

- 来自

- 中国

|

布局布线时间减少近70%---Vivado在复杂FPGA设计中大显身手

在产品的系统架构设计中,对FPGA设计的功能和质量都提出了更高的要求。单片FPGA设计需要支持更高的数据带宽,支持更多的产品feature。同时,由于项目进度的要求,又需要缩短开发周期,确保产品质量。Xilinx的Vivado开发工具很好的满足了我们的设计需求,使得我们的产品得以在保证项目进度的前提下高质量地发布。在此,分享一下在整个项目的开发过程中,Vivado留给我们的深刻印象的瞬间。

布局布线时间减少近70%

我们的项目是设计高清的视频会议系统。 项目选用了Virtex7系列中xc7vx485t作为目标器件。在设计中,需要使用3路PCIe Gen2 x8接口,3组64bit DDR3 1600Mbps接口;而由于设计本身的特性,对Block RAM资源的使用非常大,90%以上的Block RAM Tile被使用(如表1);同时,DSP Slices也占用了大约70%。因此,较大的资源使用对综合和布局布线提出了更高的要求。

表1:

Site Type

| Used

| Loced

| Available

| Util%

| Block RAM Tile

| 940.5

| 0

| 1030

| 91.31

| RAMB36/FIFO

| 568

| 12

| 1030

| 55.14

| RAMB18

| 745

| 0

| 2060

| 36.16

|

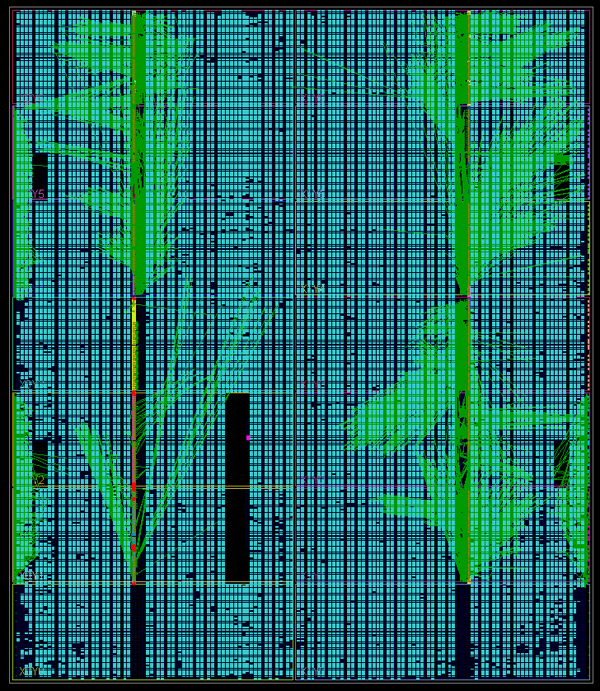

项目最初使用上一代工具PlanAhead来完成布局布线等实现过程。单次布局布线过程需要大约8小时左右,而且实现的结果也常常会有违背时序约束的情况。这极大的影响了调试的进度。当我们将设计移植到Vivado环境下运行时,情况有了令人惊喜的改变,单次实现过程只需要2个半小时到3个小时左右,比较之前减少70%的时间。而且,几乎每次实现都能满足时序约束。FPGA设计的生产力得到了很大的提高,加速了FPGA和软件调试,集成的进度。在Vivado下打开设计实现后的布局布线图(如图1),可以看到各资源放置紧密而有序,布局布线相当整齐合理。所以,可以说Vivado提供了一个针对高密度,大规模设计的有效解决方案。

功耗降低20%

Vivado对器件功耗的改善也给我们留下了深刻的印象。由于设计规模较大,外部高速接口较多,功耗一直是比较令人感到担心的问题。虽然,我们在设计中采用了一些降低功耗的方法,但是收效甚微。静态功耗达到25W以上,这对于整个系统的散热和结构来说,都是不可接受的。在我们一筹莫展之际,Vivado 2013.1带给了我们另一个惊喜。在使用Vivado 2013.1产生Image文件进行测试后,我们发现器件静态功耗奇迹般地降低到了20W左右,一下解决了我们的问题。可见,Xilinx不断在优化Vivado使其更好的符合器件特性,满足客户需求。

比前一代工具更方便、更易用、更强大

相比于之前工具,Vivado对Tcl语言的支持是一大特点。Tcl命令的使用方便了用户找到关键节点,路径,在代码和网表之间进行交互调试。特别是我们使用report_xxx Tcl命令能帮助我们获得很多设计中的有用信息。而使用Tcl文件,对于工程管理,环境设置也启到了很好的作用。

XDC约束文件比较之前的UCF文件,更符合业界的标准。在项目中将时序约束,管脚约束以及不同IP的约束分别写在几个XDC文件中,更清晰明白,有利于分析。而XDC的语法又与Tcl命令一致,使得学习和使用都方便很多。

让Vivado加速你的设计

最后,跟大家分享一些小建议或Tips:

1. Vivado使用了全新的综合引擎,更适合7系列器件特性。因此,在XST下综合成功的源文件在Vivado下有可能遇到问题,请需具体分析;

2. 对于时序紧张的设计,Implementation时建议使用Performance_Explore策略;

3. 不建议使用Incremental compile,有可能对时序有负面影响;

4. 不建议使用Implementation时的Power Opt选项;

5. 熟练掌握常用的几个Tcl命令会让Vivado工作起来效率更高;

6. 仔细检视在’Open Synthesized Design’和’Implemented Design’下的各个报告,这些报告对于发现问题,解决问题很有帮助。

以上就是我的一点经验分享。希望能对你有所帮助,相信Vivado能在你的设计中帮助到你。也希望Xilinx不断优化Vivado,带给广大FPGA工程师更多的惊喜和美好的感受。希望Vivado越来越完善和强大。 |

|

|

|

|

|