|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

[导读] 1月10日,由电子发烧友网主办的FPGA技术沙龙顺利开展。本次沙龙邀请的是Altera代理商骏龙科技FAE张亚峰,嘉宾在沙龙现场为听众详解了“SDR源同步接口时序约束”。听众均来自车载系统、测试仪器、LED显示、无线通信等高新技术厂商,甲骨文、中兴通讯、迈瑞生物医疗电子、天和时代及创凯电子等相关工程师悉数到场。

关键词:ETD同步接口时序约束FPGA

1月10日,由电子发烧友网主办的FPGA技术沙龙顺利开展。本次沙龙邀请的是Altera代理商骏龙科技FAE张亚峰,嘉宾在沙龙现场为听众详解了利用Altera Quartus II软件实现“SDR源同步接口时序约束”。听众均来自车载系统、测试仪器、LED显示、无线通信等高新技术厂商,甲骨文、中兴通讯、迈瑞生物医疗电子、天和时代及创凯电子等相关工程师悉数到场。

会议主要围绕以下三大主题展开:源同步接口介绍;SDR输入接口约束;SDR输出接口约束。

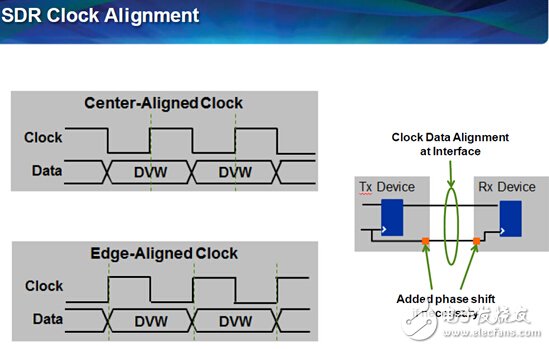

张亚峰表示同步比异步接口能得到更好的信号完整性及更低信噪比,然后讲解了Clock与Data的两种关系,即边缘对齐模式和中心对齐模式。

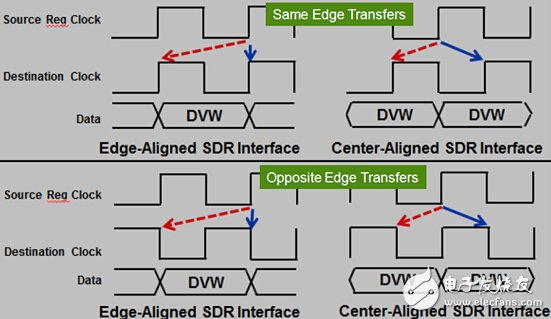

随后针对边沿对齐方式的同沿传输和异沿传输的分析做了进一步解析,模型如下,红色虚线为保持时间,蓝色实线为建立时间。

一般而言,如果设计中只采用同沿传输方式,就必须对异沿传输方式做一个false的例外约束;而相反的,如果设计中只采用异沿传输方式,那么必须对同沿传输方式做一个false的例外约束。张亚峰指出同沿传输是常用方法。

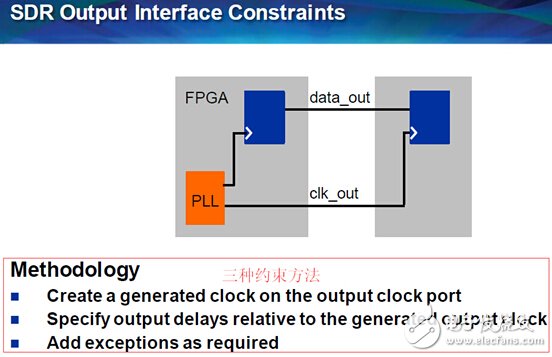

另外,张亚峰介绍SDR源同步接口约束方法主要有三种:时钟clock约束;IO的input /output delay约束;时序例外。

而输出时钟约束也有三种方法:公共数据发送,PLL生成,DDIO提醒。

对于嘉宾演示的内容,现场听众也给出了不少问题与大伙一起讨论。

问:在实际操作中,三种方法怎么选?

答:公共数据发送方法适用于低速设备;后接DDR处理器,需要调整的,选择PLL方法;一般推荐使用锁相环(PLL)方法,在不够用的时候,可以选择DDIO方法。

问:设置false路径有无考量因素?

答:设置flase路径主要是让实现工具在布局布线时不考虑这个路径,那么在同等条件下,就可以把一些走线资源让给关键路径,帮助达到时序收敛。不会对系统性能造成影响。

沙龙结束后,嘉宾与所有听众合影留念。

|

|