基于Altera FPGA的千兆以太网实现方案(2)

|

- UID

- 1029342

- 性别

- 男

|

基于Altera FPGA的千兆以太网实现方案(2)

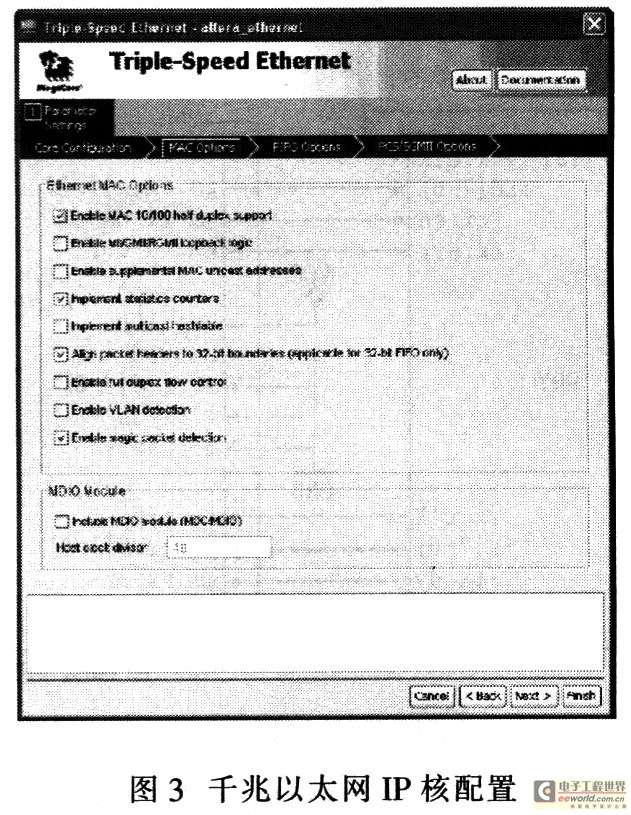

3.2.3 千兆以太网IP核 Altera提供三态以太网MAC控制器IP核,可实现单条或多条吉比特以太网链路,通过交换机或路由器可与任意以太网端口相连。其配置界面如图3所示。

整个配置界面可将IP核配置为所需模式并进行IP核参数设置,将IP核设置为千兆以太网MAC模块,内部提供FI—FO模块。可选的PCS模块由PHY器件提供,这个界面分为4个配置页面,描述如下:

- Core Configuration:核配置选项,配置以太网功能模块,是否包含PCS模块、FIFO模块,配置接口类型、端口数等;

- MAC Options:MAC配置选项,配置MAC模块功能;

- FIFO Options:FIFO存储器选项,可设置FlFO存储器类型以及存储器数据长度;

- PCS/SGMII Options:物理介质接入层模块配置页面,配置物理层。

- 相应的接口信号包括:控制接口信号,复位信号,MAC系统端信号(包括接收接口信号和发送接口信号),MAC以太网端信号(包括GMII模块信号和PHY管理接口信号)。

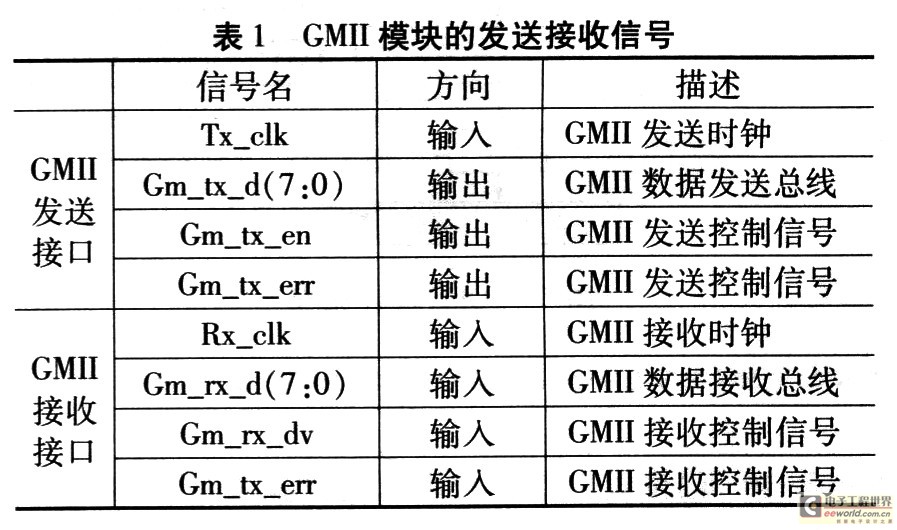

表1中描述了MAC以太网端GMII模块信号、接口信号,其余信号参考千兆以太网用户手册。GMII模块的接收信号一般直接连到PHY器件,负责与PHY器件的数据交互,其信号与PHY器件接口一一对应,如表1所列。

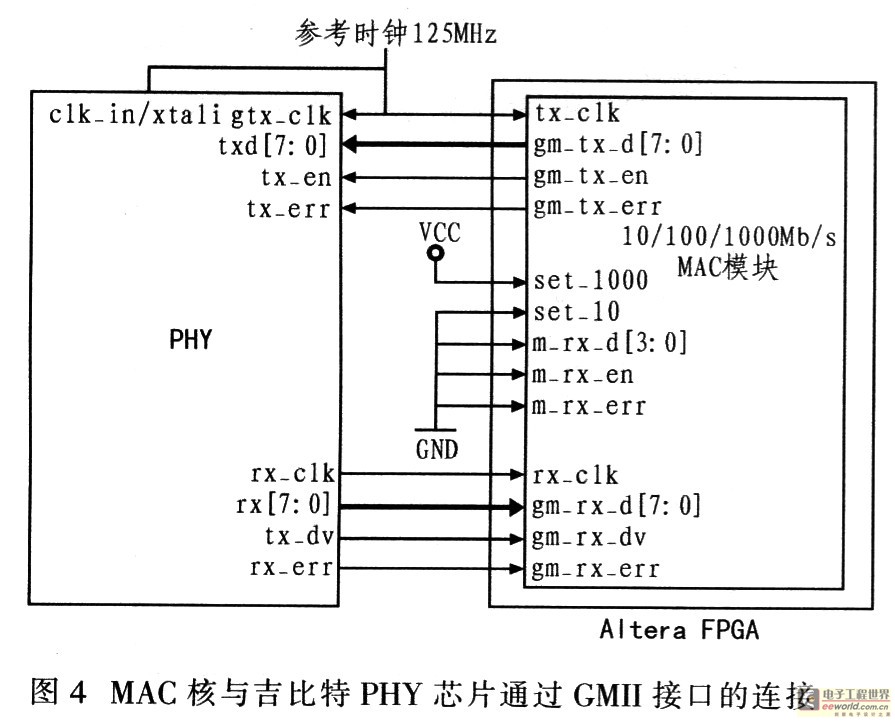

4 物理层(PHY)器件 Ahera公司的千兆以太网MAC核默认支持的物理层器件有支持10/100 Mb/s的National DP83848C,支持10/100/1 000 Mb/s的National DP83865,Marveil 88E1145以及支持双物理层和10/100/l 000 Mb/s的Marvell 88E1111。在此,选择National DP83865为PHY器件。

MAC核与吉比特PHY器件通过GMII接口的连接如图4所示。

DP83865是National Semiconductor公司的全特性物理层收发器,集成了PMD子层以支持10BASE-T,100BASE-TX和1000BASE-T以太网协议,具有超低功耗,3.3V或2.5VMAC接口。

5 开发环境

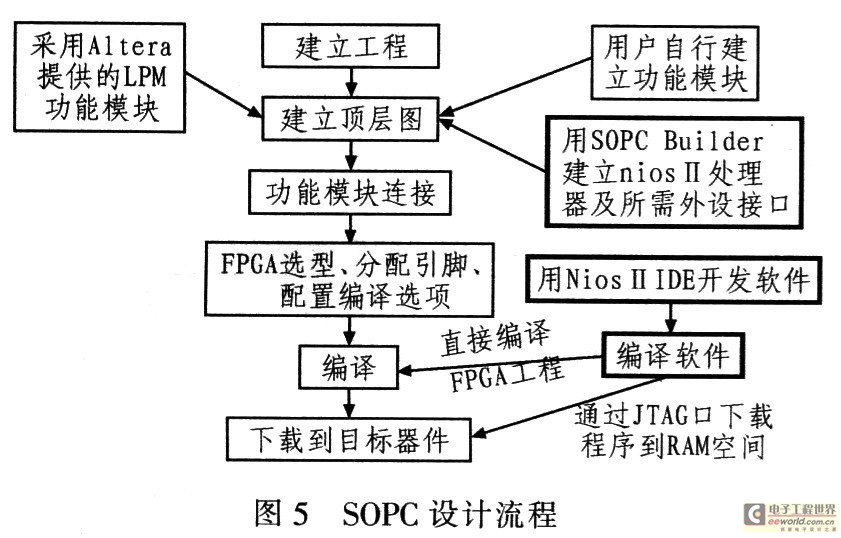

利用Ahera强大的SOPC Builder系统开发工具和Quar-tusII软件设计,基于QuartusII和niosII的SOPC设计流程如图5所示,SOPC开发流程比FPGA的开发流程(细线框)多增加处理器及其外设接口的定制步骤和软件开发步骤(粗线框)。这些新增加的步骤在SOPC Builder,niosII IDE工具的协助下能够轻松完成。

6 结语

使用千兆网系统可直接将处理的高速信号从网口发送给远端处理计算平台,节省功率放大器和高频电缆等,减少投入,加强系统的集成性和可靠性,更便于设计人员的调试,且接口更具通用性和扩展性。 |

|

|

|

|

|