|

- UID

- 863084

|

第一节 系统设计

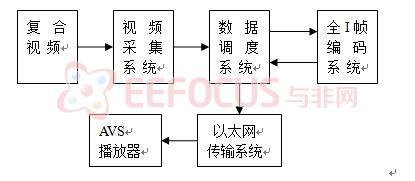

本项目基于FPGA平台完成CIF分辨率图像的实时采集、AVS全I帧压缩编码,和网络传输。本项目主要由视频采集系统,数据调度系统,I帧编码系统和以太网传输系统构成,其实现框图如图1-1所示。

视频采集系统主要完成将复合视频解码成YUV(4:2:0)数字视频,为AVS 全I帧编码准备好视频数据。

数据调度系统主要完成向I帧编码系统提供原始数据,同时将编码后的码流传输到以太网传输系统。视频数据吞吐量大,带宽高,涉及到低速存储器(如DDR)和高速存储器(如FPGA内部RAM)之间大量的数据交换,成功的数据调度策略是实时实现编码的关键技术之一。本系统包含实验室设计的DDR控制器IP核和数据调度IP核。

图1-1 系统设计框图

I帧编码系统主要完成AVS视频I帧实时编码,整个系统包括帧内预测模块,变换量化熵编码模块和控制模块。整个系统使用硬件描述语言独立设计完成。

以太网传输系统主要完成对AVS码流的打包,传输到PC机。本系统包含实验室设计的以太网控制器IP核和网络传输协议IP核。

PC机上的AVS播放器采用DirectShow架构,基于本实验室完成的AVS解码器设计了AVS实时播放器,用来验证AVS编码系统的实时编码能力。

第二节 数据采集与数据交换

前端视频采集模块采用TVP5150PBS视频解码器将输入的PAL视频信号进行转换成数字YUV(4:2:2)信号,输出格式为ITU-R BT.656。

系统上电后,FPGA通过IIC总线对TVP5150解码器进行初始化配置,接通复合视频信号后,TVP5150即可正确输出8位数字YUV视频信号至FPGA。由于接收的视频信号为ITU565格式,视频信息仅由8位视频信号组成,没有独立的行、场同步信息,所以,FPGA需要从接收的8位视频信号中提取行场同步信号,并将相邻8位数据(亮度、色差信号)转换成16位视频信号。

转换后的16位视频信号经DDR SDRAM控制器写入到外部DDR SDRAM存储器中,系统采用的DDR SDRAM存储器容量为16M*16bit,利用迸发模式,将接收的一行视频信号存储到DDR SDRM的一行,则一帧视频信号可存储器在DDR 的一个Bank空间。

视频编码时,按照宏块顺序从DDR 中读取数据,即第一个宏块数据为DDR SDRAM中的第1行至第16行、列地址0至15的前16个地址数据,第二个宏块为DDR SDRAM第1行至第16行、列地址16至23的数据内容,其余宏块读取地址依次类推。 |

|