利用基于FPGA 的仿真平台简化SoC IP 验证

|

- UID

- 1023229

- 来自

- 中国

|

利用基于FPGA 的仿真平台简化SoC IP 验证

典型的系统级芯片(SoC)设计不仅需要获取或开发IP,而且还需要完整的系统级验证和后端设计。现在,越来越多的SoC 设计师通过设计仿真来执行功能验证,以避免代价高昂的ASIC 重复投片。

仿真的方法之一是选择一种基于商用FPGA 的仿真平台,以便在现实环境中验证SoC 的IP。像Altrabit Networks 公司这样的仿真平台供应商可以从两方面帮助设计师。一是通过基于FPGA 的原型验证SoC IP;二是允许他们并行开发基于实时操作系统(RTOS)的软件,从而使芯片设计工程师与固件工程师一前一后地工作,以获得期望的结果。

目前,领先的FPGA 包含复杂的IP,如预先被构建在FPGA 结构中的RISC 处理器、高速串行/解串器和DSP 模块等。此外,它们支持多种高速I/O 接口以实现下一代总线接口,如PCI Express、HyperTransport、RapidIO 及联网和存储器接口。这些特性使得新一代PFGA成为实现基于FPGA 的SoC 解决方案或验证ASIC SoC 功能的理想选择。

需要考虑的一件事是新上市的复杂FPGA 一般都比较昂贵。因此,你必须进行混合和匹配。例如,将高性能IP 整合在一个复杂FPGA 中,而低速外设可以用一款更便宜的FPGA 来实现。这种方法比传统的高成本仿真系统更经济,因为后者不仅昂贵,而且太复杂,不便于使用。

对SoC 设计进行清楚的分割是设计师应当谨记的关键要素。诸如CPU、存储器和高速逻辑等任务需要一个复杂的FPGA,而低成本的外设可以由更便宜的FPGA 来实现。如果将这两种FPGA 通过一条基于标准的外设总线来连接,那么这种分割是清晰的。所谓标准外设总线是指在ARM CPU 中可以被用来实现AMBA 总线;在PowerPC 架构中又可用来实现片上外设总线(OPB)。当IP 频繁改变时,只有包含此变化的FPGA 需要重新配置。

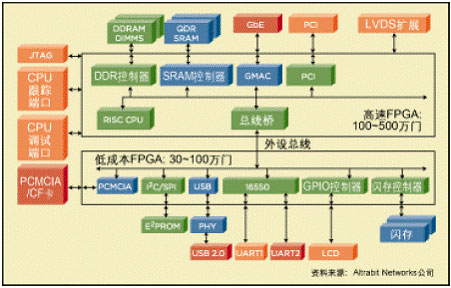

如图1 所示,Altrabit 的芯片验证仿真平台包含2 款FPGA。其中,高速FPGA 包含硬核IP模块,如RISC 微处理器、高速串行/解串器和MAC/DSP 等;它还集成了高带宽外设,如DDR SDRAM 控制器、PCI-X、千兆位以太网 MAC、零总线翻转(ZBT)SRAM 等,以获得最高的性能。该FPGA 还包含桥接逻辑,用于将处理器总线转换成外设总线,如ARM 内核的AMBA 或PowerPC 架构的OPB。

诸如PCI 总线、USB、UART 及PCMCIA 等其它低速外设则由更便宜、更低密度且适合大批量生产的FPGA 实现。这种分割方案可以节省高速PFGA 的许多门资源,并把它们用于客户的定制逻辑。这个基于FPGA 的仿真平台还提供了几个连接器,以用于FPGA 配置、调试和扩展I/O(包括用于用户自定义IP 的LVDS 信号对)。例如,PCI Express 等新兴的串行总线可以被实现,而且该接口可以被连至扩展连接器,以从物理上终结总线。

在典型的SoC 设计中,因为混合信号的复杂性问题,物理层(PHY)器件是无法集成的。所以,如果在FPGA 仿真平台上能提供一系列物理层器件,那么SoC IP 验证将因此受益。不过,设计者必须谨慎确保物理层器件在比正常工作时低得多的速度下能正常工作。

这种FPGA 方法为设计者提供了相当的自由度和必需的灵活性,允许他们采用来自新思、明导资讯、Xilinx、Altera 等第三方供应商的IP,并在ASIC 或FPGA 投入大批量生产之前,在同一硅片上混入他们自己设计的逻辑。

这增大了器件在第一次投片时通过验证的可能性。此外,设计师能获得额外的好处,即在打造芯片解决方案时能并行开发应用软件。

SoC 可能包含PowerPC、MIPS、ARM、Tensilica 或ARC 处理器;以及几个支持2.5 Gbps的高速I/O 通道、DDR 存储器控制器、高性能PCI/PCI-X 总线和调试支持功能(如JTAG 接

口)。

原型仿真平台是SoC IP 验证的核心。通过允许在开发周期的早期编写固件/应用代码,它可以加快开发时间,并避免多次投片所要花费的时间,包括后端设计、后芯片验证的时间以及制造的交货时间等。最终,它能将整个开发周期缩短一半。

对执行IP 验证的设计师和从事软件开发的嵌入式软件设计师而言,该平台是低成本的。它最吸引设计师的地方在于这种硬件/软件开发工具的易用性和低成本。此外,与其它方法相比,类似这样的一套完整开发平台能帮助设计师减少一半的验证时间并维持最低的设计成本。

作者:Ashraf Dawood |

|

|

|

|

|