|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

TOP7 程序存储器电路

程序存储器主要用于系统运行时,将采集的数字语音信号暂时存储在RAM中以备后续的处理。由于采集的数据不是太大,扩展32k的程序存储器即可满足要求。因此本系统只用到CY7C1021的低32k字空间,将DSP的地址线的低15位与CY7C1021的地址线引脚相连,而地址线的1卜18位通过一个数字逻辑电路后用于寻址CY7C1021的低32k字空间。电路原理图如图3.9所示。

Y7C1021主要电路原理图

图3.10是CY7C1021读和写信号数字逻辑电路。图中,DSP的DSP—R/W和DSP—MSTRB引脚通过或门后的输出作为SRAM的写信号,DSP—R/W的非和DSP—MSTRB引脚通过或门后输出作为SRAM的读信号。

图3.1l是CY7C1021的第16位地址引脚数字逻辑电路。图中,DSP A15经过一个非门作为二四译码器SN74LSl39AD的使能信号,DSP A16和DSP A17经过译码器后输出端Yl与Y2的非通过一个与门后的输出作为SRAM的第16位地址线。因此,低32k的SRAM映射到DSP程序空间的0X1 8000__oXlFFFF。

数据存储器电路

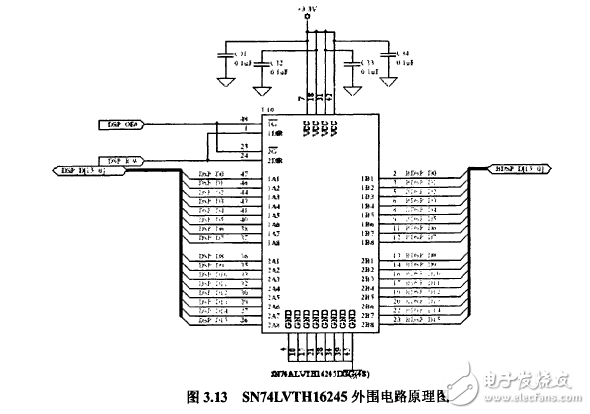

数据存储器主要用于存储编译后的系统软件的数据,用于语音识别系统板上电自举。选用flash芯片,是因为flash芯片是电可擦可写芯片,可以在线对flash进行操作,修改应用程序方便。地址缓冲器和数据缓冲器电路连接分别如图3.12和3.13所示:

SN74LVTHl6244外围电路

SN74LVTHl6245外围电路原理图

|

|