|

- UID

- 1023230

|

1 引言随着现代通信技术的不断发展,对频率源的要求越来越高。一方面,由于通信容量的迅速扩大,使得通信频谱不断向高端扩展;另一方面,由于频谱资源的相对匮乏,必须提高频谱利用率,进而对频率源的频谱纯度和频率稳定度都提出了更高的要求。

在无线通信领域中,为了提高频谱利用率,现代通信系统对频率合成器的精度、频率分辨率、转换时间和频谱纯度等指标提出了越来越高的要求。频率合成的方法主要有直接频率合成(DS)、间接频率合成(PLL)和直接数字频率合成(DDS)等方案。直接频率合成体积大、成本高, 有较多的杂散输出,这些因素限制了它的使用。间接频率合成PLL虽然体积小、成本低,但是其相位噪声、分辨率、转换速度等指标之间的矛盾也限制了其使用范围。采用可变参考源驱动的锁相频率合成器是解决这一矛盾的一种较好的方案,但可变参考源的特性对这一方案是至关重要的。作为一个频率合成器的参考源,首先应具有良好的频谱特性,即具有较低的相位噪声和较小的杂散输出。

2 X波段频率合成器主要技术指标和方案分析2.1 主要技术指标频率范围

| X波段(13.2~13.5GHz)

| 步进

| 1MHz

| 相位噪声

| -65dBc/Hz@1kHz

| 杂散

| -50dBc

|

2.2 方案分析通过分析X波段宽带频率合成器的性能指标要求可知, 工作频段、步进频率及相位噪声指标要求是确定基本方案框架的关键, 所以由此入手选择方案。由于要求的输出频率高、步进小,考虑到直接采用单一锁相方案,为了实现1MHz的步进,参考频率取1MHz,这样倍频次数最高高达12500, 达到相位噪声指标要求。实验采用了PLL的方式,提高鉴相频率,图1是基本实验方案图。

PLL频率合成器由D数字频率合成器作为参考源,驱动PLL环路,在设计我们中采用Peregnine 公司的PE3236频率合成芯片构成一个PLL频率合成器。E3236时一款能够合成频率2.2GHZ的高性能集成锁相环。它由一个前向分频器,计数器,鉴相器和控制逻辑单元组成。双模分频器对VCO频率10分频或11分频,这取决于模值的选择。计数器R和M分别对参考频率和前置分频器再分频,分频倍数为20-bit寄存器存储的整数值。另一个计数器A用在模式选择逻辑理。鉴相器产生高频和低频的控制信号。控制逻辑包括一个可选择的芯片接口,数据可以通过串行总线,并行总线或到导线连入接口。这里还有各种操作和测试模式以及锁相监测。

图1 PLL基本方案图

在锁相环路之间加了带通滤波器,此滤波器在系统的杂散抑制方面有很大作用。压控振荡器为Hittite公司的HMC401VCO,其输出频段覆盖X波段为13.2~13.5GHz 。将VCO的输出分频后反馈至鉴相器,在选择分频次数时,应注意所选用分频器对输出信号的其它次谐波抑制,以免其出现在输出频段内导致误锁的情况出现,我们选用了Hittite公司的8次分频器HMC494LP3,功率较大的分谐波为三次谐波,离所需频带较远,可用低通滤波器滤出。最终VCO输出的频率范围为13.2~13.5GHz。

2.2.1 相位噪声分析PLL实际上是一个分频系统,理论上输出相噪应该以分频比N相对于时钟相噪优化20lgN。当PLL用于倍频时,理论上经PLL倍频N /R倍, 相噪恶化应为20lg(N /R)。但在实践中发现, 这样计算出的相位噪声与实测结果不相符。工程中应用的分频器大多是数字计数分频器, 数字电路对相位噪声将会带来额外的恶化, 从而抵消了分频对相噪的优化。所以在实践中我们一般采用如下公式来计算相噪的恶化:

L(dB)= 20lg(fo/fc)=20lgN dB (1)

上式计算的结果与实际结果很相近。也就是说R分频器没有优化相噪, 他本身带来的相噪恶化与分频优化基本相当。当要求频率跳变步长很小时, 如果只使用PLL来实现, 则鉴相频率就要取得很小, 由(1)可知相噪的恶化必然很严重。

另一方面,锁相中的鉴相器有一定的噪声基底,锁相源噪声与鉴相频率、PD噪声基底和输出频率或分频比N的关系可以表示为

L0(1Hz)= Lfloop(1Hz)+10lgN+10lgfo dB (2)

其中L0(1Hz)为1Hz带宽内的PD噪声基底,N=f0/fd,f0为输出频率,fd为鉴相频率。可以看出, 无论从PLL的相噪和鉴相器的相噪基底出发分析相位噪声指标均满足要求。

2.2.2 杂散PLL的杂散来源主要有:PLL鉴相频率 的泄漏。PLL本身相当于一个窄带高Q值的跟踪滤波器,大部分的远端杂散都会被抑制的很好。这里我们关心的是落在环路带宽内的杂散分量,这样的窄带杂散水平通过调整的杂散抑制度可以达到比较好的抑制,可以初步得出实现杂散抑制为-50dBc是可能的。无论采用哪种鉴频鉴相器,VCO的控制电压都不可能是理想的直流电压,其中包括鉴相频率分量及其谐波分量。如果环路滤波器不能有效地抑制这些频率分量,其将对VCO进行调制,产生杂散输出。由于谐波频率远大于PLL的环路带宽,因此主要需考虑基波分量。 的泄漏。PLL本身相当于一个窄带高Q值的跟踪滤波器,大部分的远端杂散都会被抑制的很好。这里我们关心的是落在环路带宽内的杂散分量,这样的窄带杂散水平通过调整的杂散抑制度可以达到比较好的抑制,可以初步得出实现杂散抑制为-50dBc是可能的。无论采用哪种鉴频鉴相器,VCO的控制电压都不可能是理想的直流电压,其中包括鉴相频率分量及其谐波分量。如果环路滤波器不能有效地抑制这些频率分量,其将对VCO进行调制,产生杂散输出。由于谐波频率远大于PLL的环路带宽,因此主要需考虑基波分量。

3 电路设计X波段频率源的设计重点在于选择合理的PLL输出、锁相环路滤波器的设计以及电路PCB布板和电磁兼容设计。

3.1 环路滤波器的设计环路滤波器是锁相环电路中最重要的一个部分,它的性能好坏直接关系到锁相输出的相位噪声和杂散指标,锁定时间。环路对带内噪声呈低通滤波,对VCO噪声呈高通特性,所以选择环路带宽在两噪声源谱密度的交叉点附近总是比较接近于最佳状态的。环路滤波器分为有源滤波和无源滤波,当VCO的调谐电压超过鉴相器的最大输出电压时,就要用到有源环路。使用有源环路时,选择合适的运算放大器对环路的性能有很重要的影响,主要影响的参数有噪声电压、噪声电流、转换速率、偏置电流。其中噪声电压、噪声电流主要影响输出信号的相噪特性,而转换速率、偏置电流对杂散和转换时间的影响较大。此外运算放大器的偏置电压对输出信号的相位噪声影响也较大。

3.2 PCB的布板和电磁兼容设计3.2.1 优质电源和良好的电源滤波对于PLL电路,要得到频谱纯度高的信号,电源稳定度是非常主要的指标。可选用串联稳压器,做好直流电源与控制电源的去耦来减小外界信号对电源的干扰。

3.2.2 合理的布板鉴相器中充电泵的供电线最易受到噪声信号的影响,可在Vcc和充电泵的供电线上放置去藕电容。容值为0.1mF, 1mF和10mF的电容能在宽频率范围内滤出噪声。一般把较小的电容靠近PLL芯片放置用来处理高频噪声,大些的电容放远些,最好在它们之间加电感。设计时确保充电泵供电线和VCO的调谐线路远离噪声源,尽量避免在VCO调谐线路的近端排布任何信号走线,调谐电压非常微小的变化也会使一个高增益VCO产生很大的频率偏移。对VCO应采用适当的屏蔽措施,任何具有靠近VCO谐振点频率的噪声都会很容易地被耦合至VCO并对其进行调制,当输出信号的谐波能量被耦合至VCO振荡回路中时就会产生寄生输出,影响输出性能。

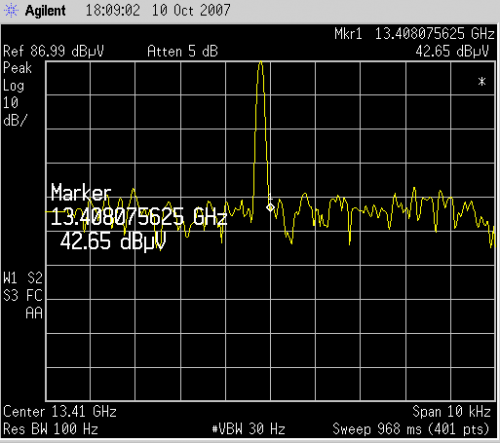

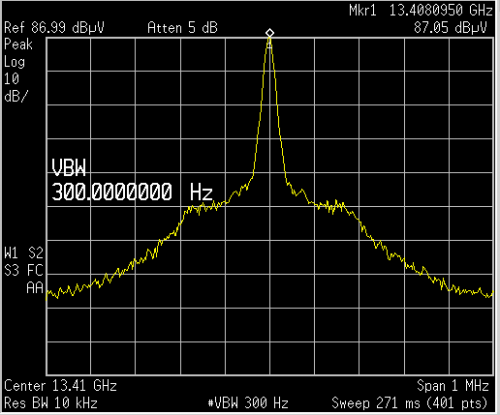

4 实验结果基于上面的理论和分析,我们研制出了输出频率为13.2~13.5GHz的频综系统,通过改变频率控制字和跳频步进,能够实现点频和以1MHz为步进的跳频输出。图2为PLL输出频点为13.41GHz时的相位噪声, 图3为PLL输出频率为13.41GHz时宽带杂散谱,鉴相频率为1MHz。由图可见,PLL输出的相位噪声达到指标所给的-65dBc/Hz@1kHz, 输出杂散也得到很好的抑制,对鉴相频率的抑制优于-80 dBc,输出杂散也得到很好的抑制。由于本实验受频率合成芯片中鉴相器噪声基底和分频器分频次数不连续的影响使得最终输出的相位噪声受鉴相器限制,故在实际应用中采用鉴相器噪声基底更低和分频次数连续的鉴相器相位噪声和杂散还可以得到一定程度的改善。

图2 相位噪声测试结果

图3 杂散测试结果

5 总结通过对X波段微波频率合成器的设计和实验工作可以看到,采用PLL 频率合成方案构成的频率合成器的指标是令人满意的。从前面的分析和实验结果可知,PLL频率合成器在相位噪声特性、杂波抑制及频率分辨率等方面相对于单一的频率合成方式都较大的优势,其更大的优点还在于相对于多环锁相和混频锁相其结构简单、调试方便、性能稳定。因此PLL频率合成方案是用于频率合成器设计的一种较好的方案,可以推广至不同的频段和不同的应用。 |

|