|

- UID

- 1023229

- 来自

- 中国

|

(5)触发条件。可以设定复杂的触发条件用以捕获相应的数据,以协助调试设计。当满足触发条件时,在SignalTapⅡ时钟的上升沿采样被测信号。

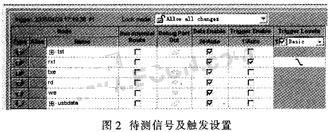

(6)设置被测信号。在SignalTapⅡ逻辑分析仪窗口,双击鼠标左键,弹出的Node Finder对话框,在filter中选择要加人STP文件的节点或总线。图2所示给出了待测信号及触发设置。

完成STP设置后,加载SAM对象文件(.sof),在Device列表中选择目标器件,点击Program Device图标进行器件编程,点击Run Analysis进行采集、分析数据,如图3所示。

4 实例分析

现以FT245BM型USB与EP2C8 0208C8N型FPGA间的简单通信为实例,具体说明如何采用SignalTapⅡ验证FPGA的设计。其顶层设计文件如图4所示。

FT245BM是FTDI(Future Technology Devices IntlLtd)公司的一种快速USB通信接口。它无需编写片内固件程序。FTDI公司提供D2XX官方驱动程序,使用D2XX驱动程序能获得更好的数据传输性能,且传输速率最大可达1 MB/s。

FT245BM的主要功能是在内部硬件逻辑的作用下实现USB串行数据格式与并行数据格式的双向转换。PC机通过USB接口与FT245BM进行数据交换,FT245BM通过并行方式与下位微控制器通信。利用单芯片实现USB与并行FIFO缓冲区的双向数据传输;通过简单的四线握手信号与FPGA等逻辑器件接口;FT245BM通过8位并行数据口D[0,7]和4位读写状态/控制口RXF#、TXE#、RD#、WR实现与EP2C8交换数据,而PC机与FT245BM间通过UISB总线传输数据。可选的外部EEPROM用于存储USB设备的特定信息,通过EECS、EESK、EEDATA来完成数据的写入和读出。

在调试中,按照上述SignalTapⅡ的使用步骤,在编译后的工程中添加STP文件,并对文件进行设置。首先设置采样时钟gclk,系统时钟采用32.768 MHz;然后添加采样深度的设置,设为2 K;最后在STP文件中将Buffer AcquisitionMode分别设为连续存储和循环采样存储两种模式进行验证。连续存储方式记录采样操作的连续过程,而在循环采样存储方式下SignalTapⅡ记录多次采样时刻数据。

当外部实验开发系统连接好后,进行编译下载。单击SignalTapⅡ面板上的Autorun Analysis按钮,启动SignalTapⅡ进行采样和分析,此时就能从SignalTaDⅡ数据窗通过JTAG口观察到来自实验板上FPGA内部的实时信号,该实例的输出信号如图5所示。

实际中将遇到许多竞争处理和不完善的地方,然而由于使用了SignalTapⅡ工具,所以能直观地看到内部的逻辑状况,这大大减少了开发周期,并能顺利地进行调试。

5 结语

Quartus中的SignalTapⅡ工具成功克服了传统逻辑分析仪的缺点,提供了一个测试器件的很好途径,还具有实时可视性,大大减少了调试、验证过程花费的时间,加快了设计周期。通过对CycloneⅡ系列EP2C8Q208C8进行实验,证实该测试手段大大提高了系统的调试能力,效果很好。但需注意的是,它是一块自主逻辑,需要占据FPGA资源。比如RAM,LE等,资源消耗量与需采集的数据量成正比。因此不能无限制地采集信号,一般采集信号的深度不大。再者,由于时钟的限制,无法看到有毛刺的现象,实际应用中也存在一定的限制。另外,SignalTapⅡ工作在JTAG方式,调试完成后,需将SignalTapⅡ移除设计,以免浪费资源。 |

|