|

- UID

- 1023229

- 来自

- 中国

|

应用VHDL语言设计数字系统,很多设计工作可以在计算机上完成,从而缩短了系统的开发时间,提高了工作效率。本文介绍一种以FPGA为核心,以VHDL为开发工具的数字秒表,并给出源程序和仿真结果。

1 系统设计方案

1.1 系统总体框图

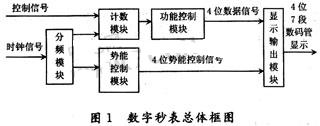

数字秒表主要有分频器、计数模块、功能控制模块、势能控制模块和显示输出模块组成。系统框图如图1所示。

本次的设计仿真选用以EP1C6Q240芯片为核心的FPGA开发板,该开发板提供了较完善的外围周边电路和信号接口,并提供了一块4位7段数码管的扩展板,为本次设计提供了硬件条件。在设计中,功能控制模块根据控制选择不同的功能状态的时间输出,通过势能控制模块和显示输出模块驱动7段数码管显示相应的时间。

1.2 系统功能要求

(1)具有时钟秒表系统功能要求显示功能,用4个数码管分别显示秒和百分秒;

(2)具有3种功能状态:系统时间运行状态,系统时间至零状态,时钟正常显示状态,通过输入控制信号可以使系统在这3个状态之间切换,使数码管显示相应状态的时间;

(3)开启时间设定、关闭时间设定可通过控制信号中的时间调节来设置,在秒设置方面每按一下,秒就会自动加1,采用60进制计数,当计数到59时又会恢复为00;百分秒设置方面每按一下,百分秒会自动加1,采用100进制计数,当计数到99时,向上进位并恢复00。系统时间可以同单独的至零信号,将数码管显示时间直接恢复到00.00状态。

2 模块功能设计及仿真

2.1 分频模块

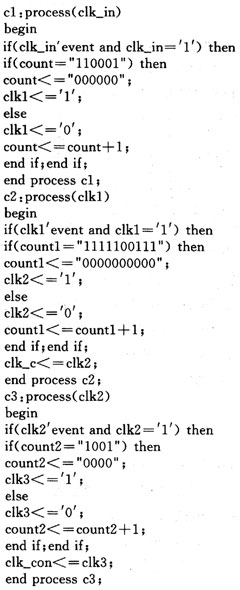

开发板提供的系统时钟为50 MHz,通过分频模块3次分频,将系统的时钟信号分为100 Hz和1 000 Hz分别提供给计数模块和势能控制模块作为时钟控制信号。该模块部分VHDL源程序如下:

2.2 计数模块

计数模块中,时钟信号是100 Hz作为秒表的百分秒输入,百分秒为100进制计数器,其进位输出作为秒的计数时钟,秒为60进制计数器。控制信号输入端的begin-stop和reset信号控制计数器的开始、停止和至零。该模块部分VHDL源程序如下,方针结果如图2所示:

|

|