|

- UID

- 1023229

- 来自

- 中国

|

绪论

信息安全的解决方案目前主要集中于采取单一的措施来保证信息的安全性,针对各种攻击手段,防范措施主要集中于信息加密技术、安全交换机技术、防火墙技术、认证技术,入侵检测技术等,这些技术从不同的方面对安全性提供了较好的保障,但各有缺点和不足,这将成为网络防护的软肋,因此,本文也尝试性地提出了一种集数据加密技术和访问控制策略于一体的信息安全解决方案。

加密算法的硬件实现具有高速率、高可靠性、高安全等特点,因此,加密算法在FPGA平台中实现是一种很好的硬件实现方案。本文在xilinx公司的spartan-3e平台中构建一个嵌入式系统来实现安全网络通信。

系统设计

该系统主要针对信息传输过程中存在信息泄露、信息篡改、非法用户入侵等安全威胁而设计的一套基于FPGA平台的网络信息安全传输系统。该系统采用客户机/服务器模式,因此,系统主要包括两个部分:客户端和服务器端。客户端作为整个系统的控制中心,根据实际需要,向服务器端发送请求,并显示接收到的信息。服务器端响应客户端的请求,发送相应信息。服务器端和客户端之间的信息都是经过加密后进行传输的,保证信息的安全可靠性。

系统服务器端设计

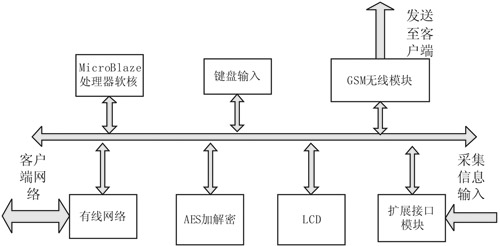

服务器端采用XILINX公司的Spartan-3e开发平台,在该平台上构建基于MicrBlaze处理器和Xilkernel操作系统的嵌入式系统,在该系统中通过定制AES加密IP、键盘IP、LCD IP、通用扩展接口控制IP并添加EDK中自带的网络控制器IP、串口IP等,服务器端的系统结构框图如图1所示。当服务器端收到经过AES加密的请求IP数据包时,在服务器端,信息需要经过AES解密处理,根据解密后信息分析并提取请求方的ID信息和IP信息,客户端的ID信息是唯一的授权证号,根据客户端的ID信息,作出相应的处理。

图1 服务器端的系统结构框图

系统服务器端设计

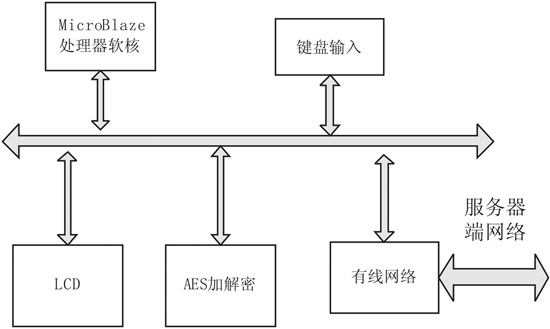

客户端同样采用XILINX公司的Spartan-3e开发平台,但该系统中只需要定制AES加解密IP、键盘IP、LCD IP并添加EDK中自带的网络控制器IP,客户端的系统结构框图如图2-2图所示。客户端作为整个系统的控制中心,当需要采集信息时,客户端经md5算法形成自己的唯一授权ID,指令信息和ID信息经过AES加密后发送至服务器端,当服务器端响应其请求后,视其身份权限做出相应处理。

图2 客户端的系统结构框图

系统具体实现

该系统采用模块化设计实现,系统包括客户端和服务器端。系统客户端和服务器端的实现都是基于xilinx公司的spartan-3e平台来实现的。

系统服务器端实现

·AES算法的硬件实现

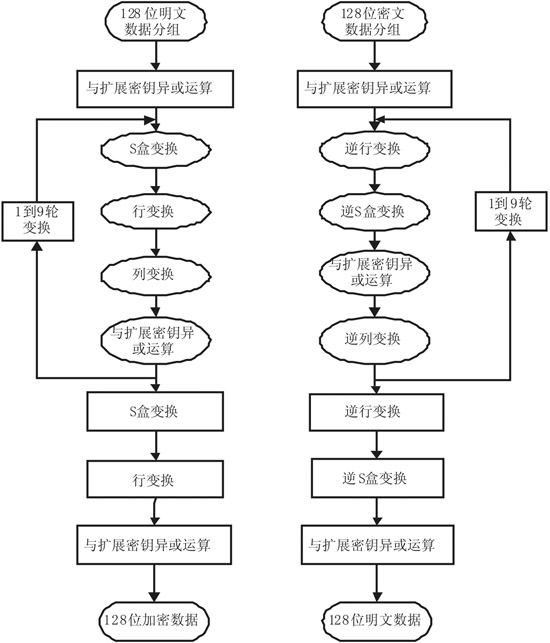

AES算法是一种迭代分组密码,采用的是代替/置换网络(SP)。AES加密算法的实现包括密钥扩展过程和加密过程。AES解密算法的实现包括密钥扩展过程和解密过程。解密过程与加密过程类似,是加密过程的逆运算,AES加解密过程如图3所示。

图3 AES加解密过程

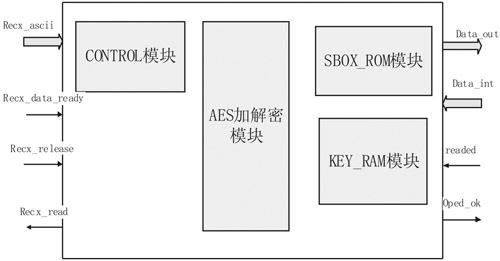

AES加解密算法通过硬件描述语言来实现,在该系统中采用VHDL语言编写代码。根据AES加解密算法的相似性,很多电路模块可以共用,其占用资源可以尽可能的少。在该系统中采用密钥长度和分组数据块长度都为128bits,输入信息都为字符型的数据,采用对字符加解密,因此,每一个字符都将对应其ASCII值输入。AES加解密实现主要有4个模块:控制模块、AES加解密运算实现模、SBOX模块、密钥操作模块,实现的框图如图3-2图所示。

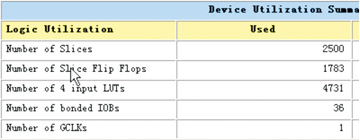

AES加解密模块的实现经过ISE 综合后占用资源利用情况如表1所示。

表1 AES加解密资源利用表

图4 AES加解密实现框图

|

|