|

- UID

- 852722

|

引言

数字信号处理器(DSP)在各领域中的应用已日趋广泛,其中TI(TEXAS INSTRUMENT)公司的TMS320系列芯片占据了主导地位。TMS320F206(简称F206)由于具有片内32K字的Flash,支持JTAG扫描端口的仿真调试,并支持程序的串行下载,便于开发设计及产品的软件升级,因而在中高档仪器开发中受到青睐。

DSP的处理速度虽然较高,但直接支持的I/O口线较少,控制能力相对较弱,因而与外部器件接口采用串行方式较为适合。常用的串行接口和串行总线有UART、I2C总线,由于I2C总线提供了较完善的总线协议,且接口电路简单,因而得到广泛的应用。目前,已有很多外围器件支持I2C接口,但多数MCU并不直接支持I2C总线,因而采用I/O口线模拟I2C的方式成为一种通用解决方案。但由于I2C总线协议的复杂性及操作管理的特殊性,仍给此类方式的开发造成了较大不便。好在文献中提出了一种按平台模式设计的、适用于80C51的虚拟I2C总线软件包,大大简化了80C51的I2C接口程序设计,使用户无需了解I2C总线协议的细节,即可实现相应的接口。文献中也给出了一种用于MSP430单片机的软件包。由于DSP尚无此类软件包,为简化DSP的此类I2C接口程序设计,本文参照文献中的设计原则,设计了一种适用于TMS320C2XX系列DSP开发的软件包。

1 虚拟I2C软件包的设计

根据文献中所提到的最佳包容性设计、后归一化设计、前归一化设计原则,软件包进行了如下定义。

(1)适用范围

① 适用主发送和主接收方式。I2C总线有4种工作方式:主发送、主接收、从发送、从接收。因实际DSP多工作于I2C总线的主方式,因而软件包设计为主方式。

② 适用TMS320C2XX系列与I2C总线外围器件的接口,支持对外围器件N字节的读写,通信方式为对虚拟节点寻址后点对点的读写。

③ 模拟I/O口线可选择4根通用I/O口线(I/O0~ I/O4)中的任意两根。

(2)软件包结构设计

TMS320C2XX系列产品,基本包括4根通用I/O口线I/O0~I/O4(由于XF仅能作为输入口线,BIO仅能作为输出口线,因而暂不考虑)。它们的输入输出方向由ASPCR的低4位来设定,相应口线状态的设定或读取由IOSR寄存器控制。但此处DSP与80C51有所不同,口线的输入输出状态不是自动切换的,且ASPCR、IOSR寄存器都不支持位寻址方式,因而在进行I2C总线工作方式模拟时较为繁琐。为避免所用寄存器其它状态位的改变,需通过较多的与、或操作来改变指定I/O口线的状态,因而本软件包与80C51的虚拟I2C软件包结构稍有不同。当然,这些均在软件包内部完成,使用者不必了解具体细节,用户接口同样简单易用。

① 软件包组成。为模拟I2C总线的操作时序,软件包中包括了2个宏定义和12个子函数。

(a)时序模拟子程序

Sendb--发送起始标志,启动I2C总线;senda--发送确认标志;

Sendna--发送非确认标志;Sende--发送结束标志。

(b)操作模拟子程序

geta--接收确认标志;sendd--发送8位数据;

getd--接收1个字节数据。

(c)数据读写子程序

wrnbyte--写入N字节;rdnbyte--读取N字节。

(d)其它宏及子函数

subsendd--根据标志位C设置模拟数据口线的状态;toggleclk--切换模拟时钟口线状态;

Xdelay--延时子程序;Sdainm--将模拟数据口线A配置为输入口线;

sdaoutm--将模拟数据口线配置为输出。

因DSP的工作频率一般远高于I2C总线的操作频率,因而这里需专用的延时子程序降低模拟时钟口线频率。本文所给出的源程序为F206采用40 MHz晶振时的情况,用户使用时可随实际情况调整延时时间。

② 软件包符号定义。软件包中包括如下符号定义:

VSDA、VSCL--分别定义了模拟数据口线和模拟时钟口线对应的屏蔽位,因DSP中对通用I/O口线的操作不能通过位操作来实现,因而仅能屏蔽位来定义,如采用IO3模拟数据线、IO2模拟时钟线,则可定义IO3为08h、IO2为04h;

RAM0--为数据暂存用的临时存储单元;

RIO--为用于保存I/O口线当前状态的存储单元;

SLA--用于保存总线上节点地址并确定传输方向的存储单元;

NUMBYTE--待发送或接收的字节数存储单元;

MTD--发送数据缓冲区;

MRD--接收数据缓冲区。

以上符号中RAM0、RIO、SLA、NUMBYTE为页内地址,与当前的页指针DP内容设置有关;MTD、MRD为绝对地址,与DP内容无关。

③ 资源占用。使用了辅助寄存器AR0、AR1、AR2、AR6、ACC、ASPCR、IOSR等资源。

④ 应用接口。软件包将wrnbyte、rdnbyte作为唯一的出口接口,用户仅需正确设置对应储存单元的内容,调用相应子函数即可:

splk #SLAR/ SLAW,SLA;写入传输节点地址及传输方向

splk #N,NUMBYTE ;写入待传输字节数

;若输出,设置输出缓冲区内容

call wrnbyte/rdnbyte

3 应用实例

3.1 器件相关功能简介

X1203是带时钟/日历电路和两个闹钟(报警)的低功耗CMOS实时时钟芯片。提供了双埠时钟和报警寄存器,在读写操作期间也能精确工作。其工作电压从2.5~6 V均可,工作电流小于1uA。时钟使用低成本的32.768 kHz晶体输入,以秒、分、时、日、星期、月和年为单位记录时间,具有闰年自动矫正功能,并对少于31天的月份自动调整;可通过设置中断标志按指定时间激活中断引脚,满足大多数用户对定时器编程的需要。该芯片引脚结构如图1所示(SOIC封装)。

其中SCL为时钟输入端,数据随该时钟信号同步输入器件或从器件输出。此引脚上的输入缓冲器始终激活。SDA端为双向引脚,用于串行数据的输入输出;具有漏极开路,可与其它漏极开路或集电极开路输出进行线"或";需上拉电阻,与SCL引脚配合,可实现400 kHz的2线I2C接口。VBack为备用电源输入端,用于VCC出现故障时向器件供电。是中断信号输出端,可通过设置报警寄存器按指定时间在该端产生报警信号;漏极开路,低电平有效。X1、X2分别为反相放大器的输入、输出端;可在X1端接入32.768 kHz的方波基准,或在X1、X2端接入32.768 kHz的石英晶振,配置成片内振荡器,在初始上电后至少有一个字节写入RTC寄存器时,时钟才开始计数。

X1203中的时钟/控制寄存器(CCR)分5部分:2个8字节报警寄存器(Alarm0、Alarm1),1个1字节控制寄存器,1个8字节实时时钟寄存器和1个1字节状态寄存器。通过报警寄存器可设置报警发生的时间,控制寄存器可使能或禁止报警中断信号的输出,实时时钟寄存器以BCD码存储了秒、分、时、日、星期、月和年,状态寄存器中保存了用于报警状态标志位及读写使能状态位。其中状态寄存器设置决定着数据是否能成功地写入。该寄存器如表1所列。

BAT标识器件当前用VBack还是用VCC工作。AL1、AL0标识Alarm0、Alarm1是否实时时钟匹配。RTCF表示实时时钟是否失效,在总电源失效后该位置1。RWEL为寄存器写使能锁存,为0表示禁止,在任何写时钟/控制寄存器之前必须将该位置1。WEL为写使能锁存,低表示禁止,通过该位写1、其它位写0,可使该位置位;通过该位写0、其它位写0,可使该位清0。只有按规定顺序设置RWEL和WEL,才能成功写入CCR。

目前,很多DSP芯片尚不直接支持I2C的接口,F206也不例外,因而这里采用2根通用I/O口线模拟I2C接口。F206与X1203的接口采用如图2所示的接口方案。

图2中在X1、X2端接入32.768 kHz的石英晶振,将时钟源配置为片内振荡器。在VCC和VBACK之间通过二极管和电阻相连,并与地间加入1个0.47 F的大电容。这样,在电源出现故障或系统电源关闭时,仍可靠VBACK端的大电容供电维持时钟芯片的正常工作。它与F206间接口采用3根口线,这里采用IO2模拟通信用的时钟信号,IO3作为数据输入、输出口线。端可根据用户需要而定,若需要时钟芯片产生中断,可将该端接到F206的中断口线上。注意其中的SDA端和端为漏极开路,必须加上拉电阻,否则不能正常通信。

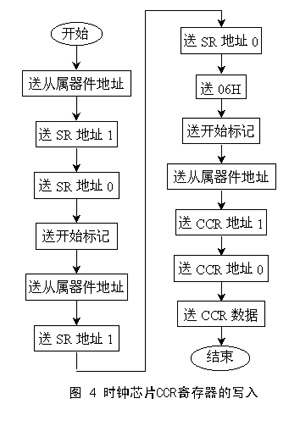

3.2 X1203的读写操作

这里仅给出F206对X1203进行读写的基本流程,如图3、图4所示,分别为对时钟芯片的读、写过程。其中进行寄存器写时,须注意SR寄存器中WEL和RWEL的设置是否正确,即首先设置WEL有效,而后将WEL、RWEL都置1,否则数据将不能正确写入。在写结束后,应将WEL、RWEL置为无效,以免产生误操作。

此外还须指出,在系统首次上电后(VBack和VCC都失效后),至少有一字节写入RTC寄存器时,系统才开始工作。在实际使用中,应首先判断SR中的RTCF位是否为1,若是,表明系统为首次使用或VBack和VCC都已失效,须对X1203至少进行一次写入操作,使其正常计数。

时钟芯片读写子程序清单如下:

.copy "init.h"

.copy "vector.h"

;以下为I2C软件包中的符号定义

VSDA .set 0008h

VSCL .set 0004h

RAM0 .set 60h

SLA .set 61h

RIO .set 62h

NUMBYTE .set 63h

MTD .set 0100h

MRD .set 0120h

setc intm ;关中断

clrc cnf ;映射块 B0 到数据存储区

ldp #0h ;页指针设置为0

clrc sxm

;数据写入使能程序段

splk #0deh,SLA

splk #3,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #03fh,*+

splk #02h,*+

call wrnbyte

splk #0deh,SLA

splk #3,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #03fh,*+

splk #06h,*+

call wrnbyte

;写入数据程序段

splk #0deh,SLA

splk #9,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #030h,*+

splk #01h,*+

splk #02h,*+

splk #03h,*+

splk #03h,*+

splk #02h,*+

splk #01h,*+

splk #21h,*+

call wrnbyte

;禁止数据写入程序段

splk #0deh,SLA

splk #3,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #03fh,*+

splk #0h,*+

call wrnbyte

;数据读取程序段

splk #0deh,SLA

splk #2,NUMBYTE

lar ar0,#MTD

mar *,ar0

splk #0,*+

splk #030h,*+

call wrnbyte

splk #0dfh,SLA

splk #7,NUMBYTE

call rdnbyte

wait: b wait

结束语

I2C总线应用已日益广泛,而其协议的复杂性和操作的特殊性又限制了推广速度。本文介绍的一种基于DSP的虚拟I2C总线软件包,简化了TMS320C2XX与I2C器件间接口程序设计,用户无需了解I2C总线协议的细节,仅需通过唯一的接口界面wrnbyte/ rdnbyte即可实现相应的接口。本文还给出了一个TMS320F206与时钟芯片X1203间的接口实例,介绍了软件包的使用方法,希望能供读者参考。 |

|