|

- UID

- 1029342

- 性别

- 男

|

离散余弦变换(DCT)

一维DCT这部分相对比较简单,离散余弦变换 (DiscreteCosineTransform,简称DCT变换)是一种与傅立叶变换紧密相关的数学运算。是数码率压缩需要常用的一个变换编码方法。因为没有现成的IP核,且语音中的优T变换是一维的,所以本文采用硬件描述语言来设计。

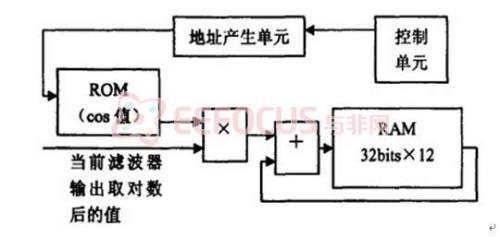

在图像处理中,DCT是先将整体图像分成 NXN像素块,然后对 NXN像素块逐一进行DCT变换。由于大多数图像的高频分量较小,相应于图像高频成分的系数经常为零,加上人眼对高频成分的失真不太敏感,所以可用更粗的量化,因此传送变换系数所用的数码率要大大小于传送图像像素所用的数码率。到达接收端后再通过反离散余弦变换回到样值,虽然会有一定的失真,但人眼可以接受。但是对于流水这种结构就不适用了。因为这种方法需要等23组滤波器组的输出结果都取完对数后刁能进行DCT运算,所以这里做了一些改动,考虑在一个滤波器组输出取对数后就开始进行DCT,修改后增加了一个DPRAM保存临时计算结果,改进后的结构如下:

实现的过程是利用Verilog编程语言实现的。

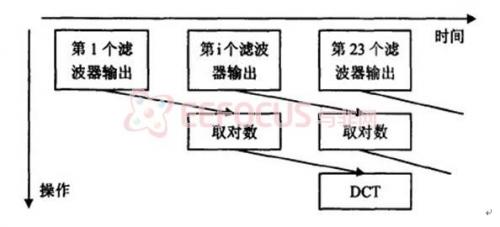

三级流水加速

三角滤波,取对数和离散余弦本来三个操作是串联实现的,现在采用三级流

水结构,使其完成其中一部分时就开始下一个操作,三个操作从一定意义上并联

起来,加快了速度。三级流水示意图如下:

4.训练模式匹配部分

对于训练识别采用HMM模型,viterbi算法,我们采用无跨越的从左至右的HMM模型,状态数为4。这里我们对viterbi算法的原始公式改进,对原始公式中∏、A、B取对数,减小乘法数据下溢问题,此外这样做有利于FPGA实现,可以减少乘法操作消耗的大量时间。由于∏、A、B都是小数,去对数后∏、A、B变成负数,所以考虑去掉符号位进行预算,对于求最大值就变为最小值。下面是对改进的viterbi算法结构介绍。

Viterbi算法改进:

- 初始化 δ[1][1]= ∏[j]+b[j][O(1)], 1≦j≦4

- 递归 δ[t][j]=min[δ[t-1]+a[j]]+b[O(t)], 2≦t≦T 1≦j≦4

φ[j]=argmin[δ[t-1]+a[j]] 2≦t≦T 1≦i j≦4

- 终止 p=δ[T][4] q[t]=4

- 路径回溯,确定最佳状态序列

q[t]= φ[t+1][q[t+1]],t=T-1,T-2,…,1

硬件结构:

分析玩上面的公式,viterbi算法最核心的部分就是第二部分递归:

δ[t][j]=min[δ[t-1]+a[j]]+b[O(t)], 2≦t≦T 1≦j≦4

下面是过程处理单元:

PE(process)单元

PE单元,用到了加比选单元,选择最小的和输出。在此之后,又用了一个数据选择器MUX,是因为第一帧的时候是特殊情况,不需要加比选单元,只要加上初始概率就行。

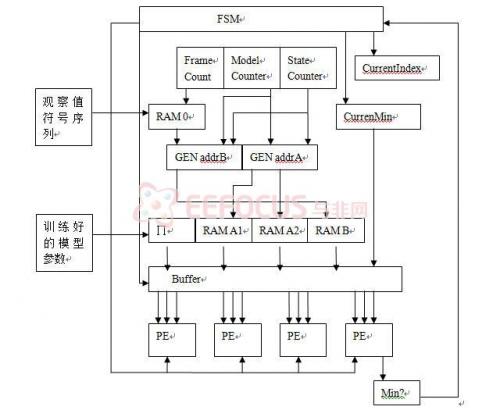

Viterbi算法的数据来源是∏、A、B,这些数据我们由matlab训练好,可以作为初始化数据保存在RAM中。观察之符号序列O由前面特征提取模块和矢量量化模块的到,作为初始化数据存入cf卡中。

下面是viterbi算法的硬件结构图如下:

FSM是基状态机控制器,Framecouter,ModelCounter和StateCounter分别是帧计数器,模型计数器和状态计数器。RAM0保存的是观察值符号序列,RAM A1和RAM A2都保存着转移概率A的值,不同的是A1保存着转移到下一个状态的概率,A2保存着停留在自身状态的概率,RAM B保存着输出概率B。GEN addrB和GEN addrA分别产生RAM B和RAM A的地址。Buffer是数据缓冲器。CurrentMin保存到当前模型为止的识别模型的最小概率,CurrentIndex保存最小概率的那个模型标号。 |

|