|

- UID

- 1023229

- 来自

- 中国

|

多功能分频器的设计与实现

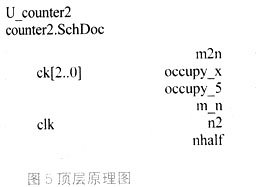

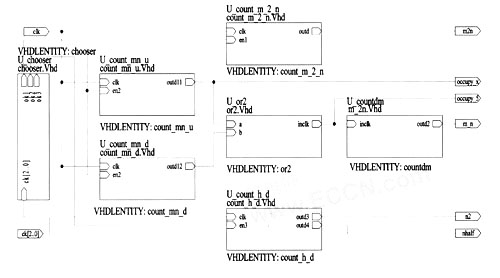

本设计使用第三方EDA开发工具Protel DXP。该开发工具支持层次原理图及VHDL语言混合设计并能进行编译、时序和功能仿真,支持Xilinx、Altera、Lattice等公司的系列 CPLD/FPGA器件,并且具有设计直观、层次性好等优点。在设计中采用两级原理图和底层VHDL语言三级结构来实现,使整个的设计以功能模块化,便于程序修改、功能升级和分频系数的设定。对于分频值的设定采取了软件设定的方法,即只需在VHDL语言程序中按照自己的需求对相应的参数作修改、设定,而且设定值的取值灵活。顶层原理图、次级原理图分别如图5、6。

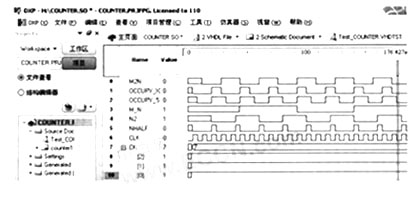

本次设计CK延时3ns后设值为111,即功能模块全部选中工作;偶数倍分频模块中模N计数器N设置为2,实现四分频;奇数倍分频模块中模2N+1计数器 N设置为1实现三分频,占空比X设置为1即分频系数为1/3,模M计数器M值设置为2实现2M*(2N+1)=12分频;N-0.5倍分频模块中N设置为 3,实现2.5分频。从方针波形中可以看出,实现了通用多功能分频器。若要得到其他值,只需修改相应功能模块的VHDL语言中的相关的参数,再进行编译、综合适配、下载即可。

器件适配及仿真波形

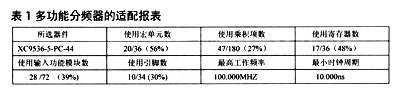

本设计采用Xilinx XC9536-5-PC44 CPLD器件实现,经综合适配后其报表如表1。

仿真波形如图7。

结束语

本文介绍了基于CPLD/FPGA的多功能分频器的设计方法,给出了原理图并用VHDL语言予以实现。结合ISP技术,基于CPLD/FPGA的分频器可以变得像软件那样灵活且易于修改、升级,能够在同一个器件内实现多种分频功能,使之成为一种多功能硬件。在产品设计、制造过程中、甚至在交付用户使用之后,仍可根据要求对器件进行逻辑重构和功能修改。在数字系统设计中,为用户提供了一种低成本的解决方案,减少了工作量和成本。 |

|