|

- UID

- 1023229

- 来自

- 中国

|

运动控制技术是数控机床的关键技术,其技术水平的高低将直接影响一个国家装备制造业的发展水平。目前,多轴伺服控制器越来越多地运用在运动控制系统中,具有较高的集成度和灵活性,可实时完成运动控制过程中复杂的逻辑处理和控制算法,能实现多轴高速高精度的伺服控制。本文选用DSP与FPGA作为运动控制器的核心部件,设计了通用型运动控制器。其中DSP用于运动轨迹规划、速度控制及位置控制等功能;FPGA完成运动控制器的精插补功能,用于精确计算步进电机或伺服驱动元件的控制脉冲,同时接收并处理脉冲型位置反馈信号。本文对该运动控制器的总体结构、硬件设计和软件设计进行了描述。

1 系统总体设计

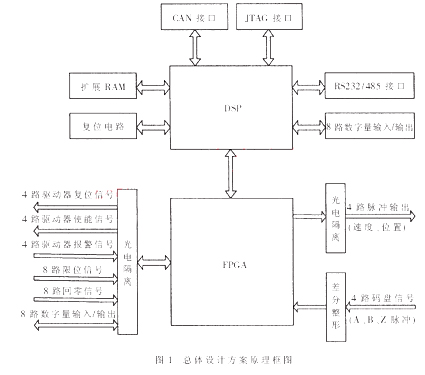

运动控制器的总体性能指标为:作为一个单独的运动控制器使用,控制信号采用数字量方式输出,能控制四轴的伺服电机;最高脉冲输出频率为4MP/s,能处理的编码器反馈信号最高频率为4MP/s;能接收和处理4路编码器反馈信号;可以处理原点信号、正负方向信号、到位信号以及急停信号等数字量输入信号;提供16路数字量输出信号和16路数字量输入信号接口。运动控制器采用DSP与FPGA芯片作为主控芯片,主要包括DSP模块、FPGA模块、FPGA外围电路模块和数字量输入输出接口模块。

采用基于DSP与FPGA的运动控制器,能够实时完成复杂的轨迹运算,而且利用DSP的高速数字信号处理功能和FPGA功耗低、主频高的优点,能充分显示该运动控制器的优点。采用DSP与FPGA相结合的运动控制器可以方便地对系统的控制策略进行修改,对控制参数进行修正,并可使设备具有良好的可靠性、可维修性,而且还降低了成本。系统还可以采用更多的智能控制策略,结构灵活,有较强的通用性,适合于模块化设计,能够提高算法效率,且易于维护和扩展。总体设计方案原理框图如图1所示。

2 系统硬件设计

2.1 DSP模块

本控制器采用TI公司的TMS320F2812为主控芯片,它是32位的控制专用DSP,内含FLASH,主频高达150 MHz,具有数字信号处理、事件管理和嵌入式控制功能,适用于大批量数据处理的场合。

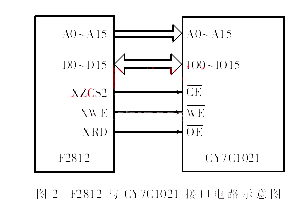

选用TI公司生产的TPS767D318芯片来实现TMS320F2812的电源设计,将5 V电源分别转换为3.3 V和1.8 V。SRAM是DSP常用的外围存储器,它具有接口简单、读写速度快等优点,所以选择大小为64 KB的随机存储器CY7C1021作为存储器扩展芯片。DSP F2812与CY7C1021接口电路如图2所示。

复位电路设计采用TI公司的TPS382x系列电压监控电路,此系列电路不需要外围电路即可组成监控电路。SCI模块用于扩展RS-232和RS-485串行通信接口;CAN模块和外部CAN工业现场总线相连;外部接口用于与FPGA连接和扩展数字量输入输出。

2.2 FPGA模块

FPGA芯片选用Altera公司的Cyclone系列EP1C6TC44C8,这是一款高性能、低功耗的FPGA。EP1C6TC44C8具有2个锁相环,包含5 980个逻辑单元,相当于12万门的规模,同时还包含了最高频率200 MHz、92 160 bit的内部RAM。该芯片所拥有的逻辑门数量、频率和引脚I/O等资源都能很好地满足运动控制器的设计要求。由于本系统的控制对象是伺服电机,所以设计中主要利用EP1C6TC44C8的I/O口设计电机控制信号的输入输出、编码器信号的输入与部分数字量输入输出。另外,该芯片在整个硬件系统设计完毕后还可以通过JTAG接口对硬件进行重配置,可以增加系统设计的灵活性。

2.3 FPGA外围电路模块

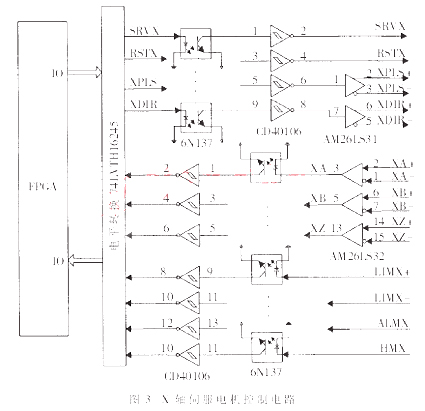

X轴伺服电机控制电路如图3所示。Y轴、Z轴、U轴伺服电机控制电路与X轴相同。

(1)输入输出开关量接口设计。输入信号主要包括限位开关信号LIMX+、LIMX-~LIMU+、LIMU-,伺服报警信号ALMX~ALMU和回零信号HMX~HMU。输出信号主要包括伺服使能信号SRVX~SRVU和复位信号RSTX~RSTU。当检测到这些信号后,确定具体触发的信号,限位信号触发,则立即停止对应电机该方向的运动,直到限位消除,电机才能在该方向继续运动;回零信号触发,则电机等待Index信号的输入后立即让电机反向运行用户设定的回零距离作为机械零点;伺服报警信号输入时,程序立即停止该电机的运动,直到用户将报警清除。

(2)输出控制脉冲电路设计。输出控制脉冲信号为伺服电机的4路脉冲控制输出信号。此控制采用“脉冲+方向”指令,由于每个控制轴分别有脉冲和方向信号,所以4路共8个输出信号。输出控制脉冲信号由FPGA输出,要先经过电平转换,将FPGA的I/O引脚的3.3 V变为5 V,再经过光电隔离,然后再经过施密特触发器整形后输出。由于脉冲和方向信号需要进行差分,所以将信号接入差动线驱动器后再输出。XPLS~UPLS为脉冲信号,XDIR~UDIR为方向信号。差动线驱动器由AM26LS31构成,该电路的功能是将输入的单极性的方波信号转化为一对极性相反的电机驱动信号,它的高阻抗输出状态在电源掉电时是有保障的。 |

|