4.3.2 Apache

Apache是世界上最通用的Web服务器之一,Apache是由一系列的模块组成,其中http_core.c是其核心模块。在Apache中模块是通过钩子函数处理客户端请求的。在Apache中用来处理请求的主要钩子如下:

post_read_request在正常请求处理流程中 这是模块可以使用的第一个钩子。

translate_name Apache用来将请求URL映射到文件系统的钩子。

map_to_storage这个钩子使得Apache 能够决定应用到这个请求的配置选项。

header_parser这个钩子检查请求的头部。

access_checker Apache根据服务器的配置 httpd.conf 检查是否允许访问请求的资源。

check_user_id模块可以通过这个钩子实现一个认证方法。

auth_checker这个钩子检查是否允许认证的用户执行请求的操作。

type_checker这个钩子针对用户请求资源的 MIME类型(可用的)的相关规则判定将要使用的内容处理函数。

fixups这是一个通用的钩子,允许模块在内容生成器之前,上述描述的钩子运行之后,运行任何必要的处理流程。

handler这是一个内容生成器钩子,它负责给客户端发送一个恰当的回复。

log_transaction这个钩子在回复已经发送给客户端之后记录事务,模块可能修改或者替换Apache的标准日志记录。

上面即为Apache对请求的处理流程。

4.4防篡改模块

4.4.1模块构建

防篡改模块构建如图5所示。

图 5 防篡改模块构建框图 4.4.2模块工作流程1、发布流程

(1)由管理员更新CF网页文件备份。

(2)通过CF将新更新的网页发送到web服务器上。

2、正常访问流程

(1)当用户访问网站的时候Web服务器收到用户发送的页面请求。

(2)防篡改模块截获页面访问请求 找到相对应的网页或者脚本。

(3)防篡改模块计算出这个网页或脚本的散列值,并与备份的散列值比较。

(4)如果相同,那么说明这个网页或者脚本没有被篡改,这次访问请求继续被正确执行。

3、被篡改访问流程

(1)当用户访问网站的时候Web服务器收到用户发送的页面请求。

(2)防篡改模块截获页面访问请求 找到相对应的网页或者脚本。

(3)防篡改模块计算出这个网页或脚本的散列值,并与备份的散列值比较。

(4)散列值不同,说明网页被篡改,访问终止,并向管理员发出警报。

5 PCIE

5.1 PCIE 总线的介绍

PCI Express是用来互连诸如计算和通信平台应用中外围设备的第三代I/O 总线技术, 第一代总线包括ISA、EISA、VESA 和微通道(Micro Channel)总线, 而第二代总线则包括了PCI、PCI- X 和AGP。PCI Express 是一种能够应用于一种设备、台式电脑、工作站、服务器嵌入式计算机和通信平台等所有周边I/O 设备互连的总线。PCIE最初由Intel发展, 并于1992年在市场发布。PCIE的体系结构继承了第二代总线体系结构最有用的特点, 并且采用了计算机体系结构中新的开发成果。它保留了原先的通讯模型和下载配置机制, 但抛弃了共享总线的方式, 采用点到点的总线连接方式。由于它提供了更高的性能特点和越来越大的带宽, 从而解决了PCI、PCI- X和AGP的许多缺点, 是以后PC发展必然采用的接口总线, 其必将取代PCI, PCI- X 以及图形加速器(AGP)。PCIE总线保留了对于PCI局部总线协议全部软件的向下兼容性, 即只要是PCIE 的卡都可以插到带有PCI的操作系统使用; 在硬件上, 两者不兼容, PCIE 取代PCI、PCI- X的并行多路总线结构, 采用了一种串行、点到点的总线连接结构, 需要的接口更少。

5.2 PCI Express模块

我们使用的是Xilinx公司的Vertex-5的 FPGA,并在FPGA上实现PCIE的接口设计。

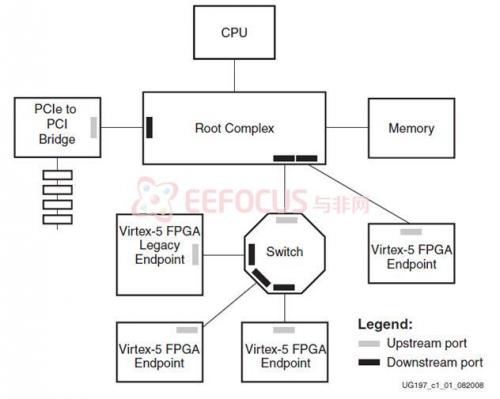

Vertex-5芯片集成了PCI Express的端点块,符合PCI Express基础规范1.1。其组成框图如图6所示。

图 6 Vertex5芯片集成的端点block

按照PCIE协议的要求,该FPGA的IP核也采用三层体系结构,即传输层、数据链路层和物理层。这三层功能模块完成了PCIE的协议转换,在传输层上给开发人员提供了非常丰富的接口。开发人员的所有开发,包括DMA传输等都是在传输层以上进行的。

传输层(transaction layer):完成TLP(数据传输包)的收发,含有虚拟信道(VC)缓冲区,具有端口仲裁、VC仲裁、流控制、数据重新排序和数据校验等功能。

数据链路层(data link layer):数据链路层的主要功能是保证在各链路上发送和接收数据包时数据的完整性。在接收端,对数据进行严格的CRC校验,如果有错误,会给发送方返回1个NAK信号。发送端具有重传缓冲区,如果收到NAK信号,则把数据重新发送1次。

物理层(physical layer):对于发送端,接收数据链路层的数据包,把这些数据进行8 b/10 b编码,送到串行发送器上;对于接收端则刚好相反,收到串行码后,先解码,然后送给数据链路层。

图7是一个PCIE系统的组成框图。包括根复合体、端点设备、交换开关、PCIE-PCI桥等,在本项目中,我们的Vertex-5开发板充当端点设备。

图 7 PCIE 系统的拓扑结构

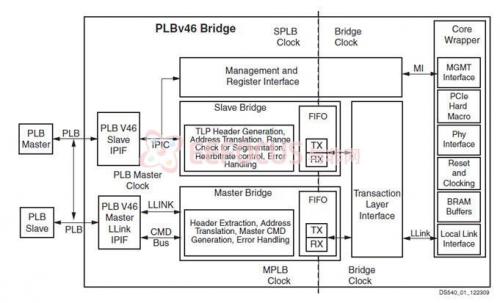

5.3 PLB桥我们在Vertex-5开发板上搭建嵌入式系统。处理器使用MicroBlaze处理器软核,采用PLB总线结构。PLB总线与PCIE总线之间通过PLB桥连接,即使用EDK下的PLBv46 IP Interface (IPIF) to logicCORE PCI Express Bridge模块。这个IP提供了PLB到PCIE的桥连接。

PLB桥提供了在传输层的PLB总线命令和PCIE TLP(Transaction Lay Packet)事务层包的相互转化。图8是PLB桥的结构组成框图。PLB桥中包含PCIE硬核端点模块。

图 8 PLBv46桥组成框图

初始化时首先要定义各个参数在配置空间的偏移地址。 #define PCIE_CFG_ID_REG 0x0000 /* Vendor ID/Device ID offset */ #define PCIE_CFG_CMD_STATUS_REG 0x0001 /* Command/Status Register Offset */ #define PCIE_CFG_CAH_LAT_HD_REG 0x0003 #define PCIE_CFG_BAR_ZERO_REG 0x0004 /* Bar 0 offset */

定义一些寄存器的32位地址偏移。 #define PCIE_CFG_CMD_IO_EN 0x01000000 /* I/O access enable */ #define PCIE_CFG_CMD_MEM_EN 0x02000000 /* Memory access enable */ #define PCIE_CFG_CMD_BUSM_EN 0x04000000 /* Bus master enable */ #define PCIE_CFG_CMD_PARITY 0x40000000 /* parity errors response */ #define PCIE_CFG_CMD_SERR_EN 0x00010000 /* SERR report enable */ #define PCIE_CFG_CMD_INTR_DISA 0x00040000 /* Interrupt Disable */ #define PCIE_CFG_BUS_MASTER_ENABLED 0x00004000 然后寻找配置空间,进行配置空间初始化,然后启用桥这样才能传递TLP数据。

6 驱动设计

由于Vertex-5开发板最终需要插在WEB服务器主板PCIE插槽中工作,要实现WEB服务器和Vertex-5开发板的正常通信,需要开发PCIE服务器端驱动。

6.1 WinDriver开发工具概述

WinDriver是美国Jungo公司出品的、用于编写硬件驱动程序的一种工具软件,主要针对ISA插卡、PCI插卡和USB这些硬件的设备驱动程序进行开发。通过运行DriverWizard能

6.2 基于WinDriver的驱动程序设计

WinDriver编程有两种模式,一种是用户模式,这种模式利用软件自身提供的驱动程序W模式适宜于用户对速度有特殊要求的情况。在一般采用用户模式。

驱动程序主要实现对设备的初始化、读写控制等操作,一般驱动程序的运行过程如图9所示。

图9 驱动程序运行流程

7 总结

上面对基于FPGA的数据安全系统进行了简要介绍。目前,我们已经完成了防篡改模块编写、网站创建、嵌入式系统硬件平台创建和嵌入式操作系统定制工作,现在正在进行PCIE服务器端驱动程序的开发。驱动程序开发完成后,会对整个系统进行调试。 |