|

- UID

- 1029342

- 性别

- 男

|

4 实验结果

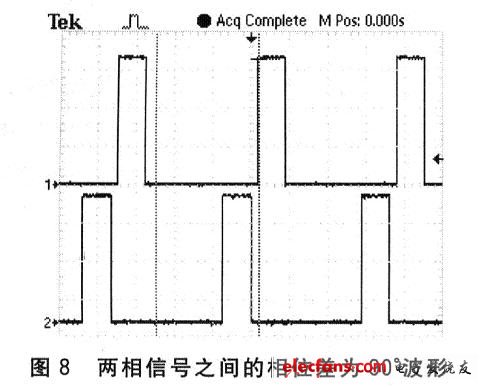

本设计采用全数字结构,易于用CPLD实现。以EPM7256为目标芯片,设计并实现了正确的数据传输。当DSP56F801输出的十六进制参数分别为频率字DBOE,相位字0403,A相的占空比字04CE,B相的占空比字04CD时,波形输出如图7、图8所示。图7给出了信号发生器A相输出信号的实测波形,信号占空比调节为20%;图8给出了A相输出信号1和B相输出信号l的实测波形,两相信号相位差调节为常用的90°。该实验结果表明,参数传输正确,波形输出良好。

结 语

SPI通信方式具有硬件连接简单、使用方便等优点,应用广泛。采取硬件和软件相结合的措施,可以确保SPI通信中数据流的同步,实现可靠通信。本文给出了DSP多SPI端口通信的设计与实现过程,讨论了其中的关键技术问题。SPI多端口通信方法基于CPLD实现,易移植,易于实现功能扩展,可广泛应用于各种采用SPI通信方式的自动化装置。 |

|