2.2 系统概要设计

2.2.1 Genesys开发板简介

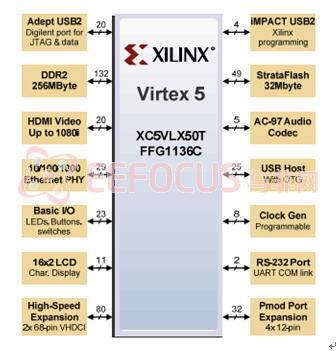

Digilent的Genesys开发板集成了功能强大的Xilinx Virtex®-5 FPGA,为广大用户带来了一个功能强大、方便实用的设计平台。其设计框图如图 3所示。

图 3 Genesys开发板的组成框图

Genesys板上还集成了千兆以太网接口、高速存储器、高分辨率音频和视频电路、以及USB主机接口等选项。Genesys开发板采用业界主流设计,无论是复杂系统,还是专用的高性能应用,Genesys都能为您提供有效的解决方案。其主要特性如下所示:

- Xilinx Virtex 5 LX50T FPGA, 1136-pin BGA package

- 256Mbyte DDR2 SODIMM with 64-bit wide data

- 10/100/1000 Ethernet PHY and RS-232 serial port

- multiple USB2 ports for programming, data, and hosting

- HDMI video up to 1600x1200 and 24-bit color

- AC-97 Codec with line-in, line-out, mic, and headphone

- real-time power monitors on all power rails

- 16Mbyte StrataFlash™ for configuration and data storage

- Programmable clocks up to 400MHz

- 112 I/O’s routed to expansion connectors

- GPIO includes eight LEDs, two buttons, two-axis navigation switch, eight slide switches, and a 16x2 character LCD

- ships with a 20W power supply and USB cable

2.2.2基于Genesys开发板的实现构想

根据上面所述的预期实现功能与技术指标,并结合Genesys开发板的资源,本设计的实现构想:

- 使用XILINX公司的Microblaze作为整个系统的中央处理器;

- 在Microblaze软核处理器系统中进行PeatLinux操作系统的移植;

- 使用FTP协议进行图像数据的传输;

- 通过有线以太网的通讯方式与FTP服务器进行连接,并下载FTP服务器里的视频数据进行播放或存储在本地的U盘上;

- 使用带有HDMI的LCD液晶显示器作为显示设备;

2.2.3 Genesys开发板上的资源利用情况

根据设计的要求,Genesys开发板上的硬件资源既能满足本设计的硬件需求又能显示出其优越的性能。表格 1为本设计在Genesys开发板上的资源利用情况。

表格 1 本设计在Genesys开发板上的资源利用情况 Genesys开发板的硬件资源 | 本设计中的使用情况 | Adept USB2 | √ | DDR 256MByte | √ | HDMI Video | √ | 10/100/1000 Ethernet PHY | √ | Basic I/O | √ | 16 X 2 LCD |

| High-Speed Expansion |

| iMPACT USB2 | √ | StrataFlash 32Mbyte | √ | AC-97 Audio Codec |

| USB Host | √ | Clock Gen | √ | RS-232 Port | √ | Pmod Port Expansion | √ |

第3章 系统详细设计

3.1 系统硬件平台设计

3.1.1 系统的硬件构成

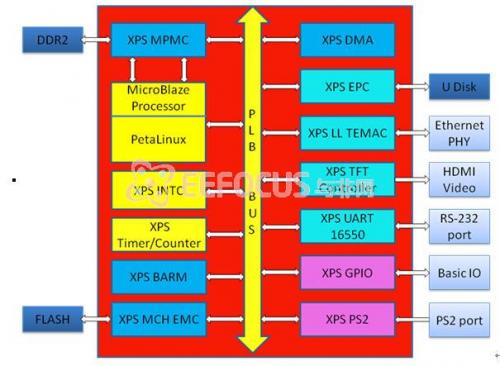

本系统的硬件设计由以下部分构成:MicroBalze处理器、中断控制器XPS INTC、XPS Timer/Counter定时器/计数器、XPS BRAM接口控制器、外部存储器控制器XPS MCH EMC、多端口存储器控制器 XPS MPMC,DMA控制器XPS DMA、外设控制器 XPS EPC、三态以太网MAC核 XPS LL TEMAC、XPS TFT控制器、串口控制器XPS UART 16650、通用IO控制器 XPS GPIO、XPS PS2等控制器组成。图4为本系统的结构框图。

其中,MicroBalze处理器、中断控制器XPS INTC、XPS Timer/Counter定时器/计数器构成了移植Petalinux基本硬件平台。多端口存储器控制器 XPS MPMC连接外部的DDR2 SODIMM,外部存储器控制器XPS MCH EMC连接外接的Flash。XPS EPC提供USB Host功能用来连接U盘。XPS LL TEMAC 核用来提供以太网接入。XPS TFT 控制器连接HDMI接口,驱动LCD的显示。XPS UART 16650 连接串口,作为移植PetaLinux的调试接口。XPS PS2 IPCore 连接PS2接口,在本设计中连接鼠标,提供用户操作接口。

图 4 系统结构框图

3.1.2 系统所需的IP核简介

为了提高设计性能和缩短设计周期,本设计将会充分利用Xilinx公司所提供的多个IP核进行开发设计。本设计中将会使用到的IP核以及使用该IP核的理由如下所述:

- 软处理器 本设计使用的处理器IP核为MicroBlaze。MicroBlaze内核是一款32位 RISC 哈佛架构软核处理器,具有丰富的、针对嵌入式应用进行了优化的指令集。MicroBlaze 拥有超过 70 种配置选项,支持从超小型嵌入式微控制器到运行 Linux 的高性能嵌入式计算机的各种配置。这种灵活性的核心在于两种版本的 MicroBlaze:针对面积进行了优化的 MicroBlaze(带有3级指令执行流水线)和针对性能进行了优化的 MicroBlaze(带有5级指令执行流水线)。

- 中断控制器 设计中,选取了XPS Interrupt Controller IP Core该中断控制器。该控制器具有如下特征:作为32bit的从设备连接到32、64或128位的PLB总线上;可配置的中断输入数目;触发沿可设置为上升沿或下降沿。

- 定时器 设计中需要使用定时器来为PetaLinux产生时钟节拍,设计中选了XPS Timer/Counter,是用于连接PLB总线上的32位定时器。该IP同时具有如下特征:作为32bit的从设备连接到32、64或128位的PLB总线上;其PLB接口支持字节使能;可编程的定时器位宽;PWM输出。

- DDR2控制器 选用XPS MPMC IP Core作为本系统的DDR2内存控制器。该控制器具有如下特点:支持SDMA;支持单速率内存(SDR)和双速率内存(DDR/DDR2/DDR3/LPDDR);支持错误检验、性能显示和寄存器调试功能。

- 片上Block RAM控制器 选用BRAM Interface Controller作为片上Block RAM的控制器。该控制器具有如下特点:支持32、64、128位的PLB接口;支持32、64、128位的内部RAM数据宽度;32bit的地址宽度。

- FLASH控制器 选用XPS MCH EMC作为外部FLASH存储控制器,该控制器具有如下特点:可作为32bit的从设备连接到32、64或128位的PLB总线上;支持多达4个的外部存储块;支持单beat传输和burst传输;支持同步/异步SRAMs和Nor Flash内存芯片。

- DMA控制器 选用XPS Central DMA Controller作为系统的DMA控制器,该控制器具有如下特点:可作为32bit的从设备连接到32、64或128位的PLB总线上;支持一个通道的源地址到目的地址的内存直接读取;提供可编程的源地址、目标地址和传输长度;参数化的本地FIFO深度和burst突发深度;支持不连续块的会输。

- U盘控制器 选用XPS External Peripheral Controller作为U盘存储的控制器,该控制器具有如下特点:可作为32bit的从设备连接到32、64或128位的PLB总线上;支持同步或异步的方式与外设通讯;可根据外设芯片来设定数据宽度;可配置的外部总线接口时序。

- 以太网控制器 选取XPS LL TEMAC作为本设计的以太网MAC控制器,该控制器具有如下特点:具有2K、4K、8K、16K、32K 字节的接收和发送数据FIFO缓存;过滤错误帧;支持多种PHY接口;全双工操作;支持VLAN帧。

- TFT显示控制器 选取XPS TFT Controller作为LCD控制器,该控制器具有如下特点:支持18bit VGA或24bit DVI;支持25MHz 时钟实现640*480分辨率、60Hz刷新率;支持PLB接口与TFT接口的两个独立时钟。

- UART控制器 选取XPS 16650 UART作为本设计的串口控制器,该控制器具有以下特征:支持PLB V4.6接口;软硬件上兼容全部16450和16550UARTs;满足所有的串口接口协议。

- 通过I/O控制器 设计中选用PLB General Pupose Input/Output来控制LED灯,该控制器可配置为单端或双端GPIO通道;每个GPIO可动态配置为输入或输出口;可生产中断请示。

- PS2控制器 本设计中使用XPS PS2 Controller作为鼠标的控制器,该控制器的特征有:作为32bit的从设备连接到32、64或128位的PLB总线上;可配置成单端或双端的PS2控制器;支持两个PS2设备,分别由两个8字节宽的寄存器控制。

3.1.3 移植PetaLinux的可行性分析

Genesy Virtex-5 FPGA Development Board开发板上面有256MB的DDR2 SODIMM、16Mbyte StrataFlash(一共32M字节)。这16Mbyte StrataFlash作为非易失存储器来存放FPGA的配置文件,单个FPGA的配置文件大小不超过2MByte,剩余30M字节供用户使用。PetaLinux一般规则下的最小配置为需要4MByte的DDR2,推荐使用16MByte的DDR2,至少8Mbyte的FLASH。因此,在Genesy Virtex-5 FPGA Development Board开发板上面嵌入MicroBlaze处理器核后,再进行PetaLinux的移植是可行的。本设计采用的嵌入式操作系统为2.6内核的PetaLinux。 |