5系统实现

本作品使用Xilinx公司的FPGA产品系列Spartan 3E,射频模块采用Ti-Chipcon公司的CC2420,工作在2.4GHz频段。程序使用Verilog语言编写,可以实现两块板子之间的双工通信,支持250kbps的传输速率。通信采用AES加密,带有CRC校验及地址验证,实现了基于FPGA的无线通信安全协议。

5.1加密算法

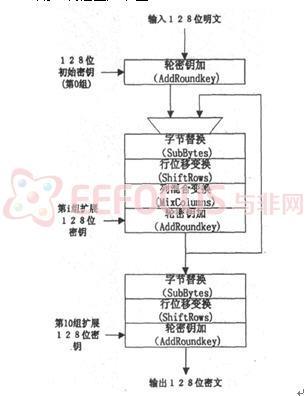

AES分组密码算法通常由密钥扩展算法和加密(解密)算法两部分组成。本作品采用128位AES加密算法。密钥扩展算法将4字节用户主密钥扩展成10个子密钥。加密算法由,字节替换,行变换,列混合,以及轮密钥加密组成。混乱和密钥扩散是分组密码算法的基本原则。流程图如下图:

图:128位AES加密流程图

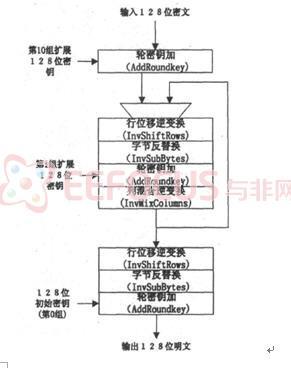

图:128位AES解密流程图

代码实现使用如下几个模块:

module aes(clk,reset,load_i,decrypt_i,data_i,key_i,ready_o,data_o); module subbytes(clk,reset,start_i,decrypt_i,data_i,ready_o,data_o,sbox_data_o,sbox_data_i,sbox_decrypt_o); module mixcolum(clk,reset,decrypt_i,start_i,data_i,ready_o,data_o); module word_mixcolum(in,outx,outy); module keysched(clk,reset,start_i,round_i,last_key_i,new_key_o,ready_o,sbox_access_o,sbox_data_o,sbox_data_i,sbox_decrypt_o);

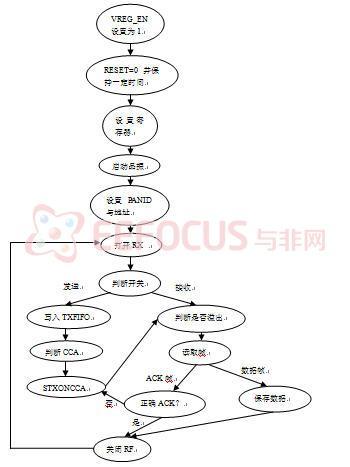

5.2通信模块

流程图如下:

|