既然决定认认真真搞FPGA,学好modelsim,那么就一路坚持下去!首先,继续摸熟modelsim仿真。

今天摸清了用Modelsim做功能仿真,综合后仿真,时序仿真。纪录下过程和对比下结果。

首先在前面的博客中,各种环境已经在前面搭建完毕,包括编译仿真库等,一会会有一个简单的各个仿真比较例子。

FPGA各种仿真概念(摘自CB书中)

1. 功能仿真(前仿真),验证逻辑功能,不用全编译,即ctrl+k就可以了。验证电路功能是否符合设计要求。这个仿真一般是必须做的。

2. 综合后的仿真,这个是FPGA综合产生的网表(会有门延时),一般是不用做的,这里要对比几个仿真结果的不同,也做一遍。

3. 时序仿真,布局布线后的仿真,这个时候就包括了布线的延时,一般这个也需要做的。

偶然找到一张笔试卷子的题目的module,就以他为例来做了:

首先写好v文件:如下:

+ 查看代码

写好testbench文件:

+ 查看代码

那么开始了

一:功能仿真

1.quartus建立工程后,编写v文件,ctrl+k,无错误(当然注意风格)

2.编写testbench文件

3.建立sim1仿真工程,在sim有单独的sim1的文件目录,将v和testbench拷贝到sim1

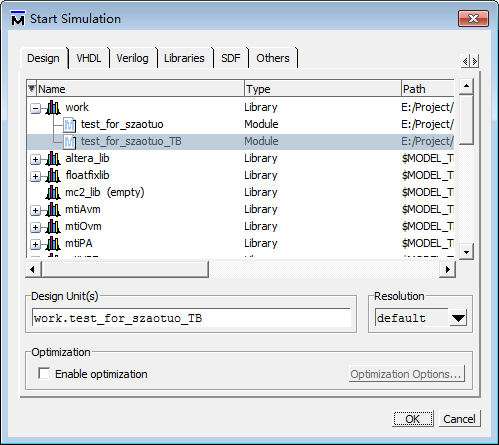

这里我们没有用到altera的IP核,所以在library那里可以不用设置路径,如果有用到的话,就要指定路径了。

4.仿真,这个前面没什么区别,注意去掉 Enable optimization

5.添加信号,run 500ns

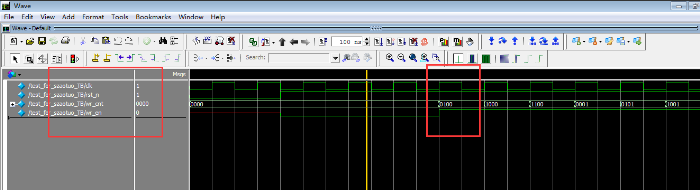

可以看到,在wr_en拉高的时候,cnt立马就有输出,这是没有任何延时的,是纯粹的功能仿真。功能仿真需要文件:v源文件+testbench+指定仿真模型(altera仿真库等,等下就有用到)

二:综合后的仿真

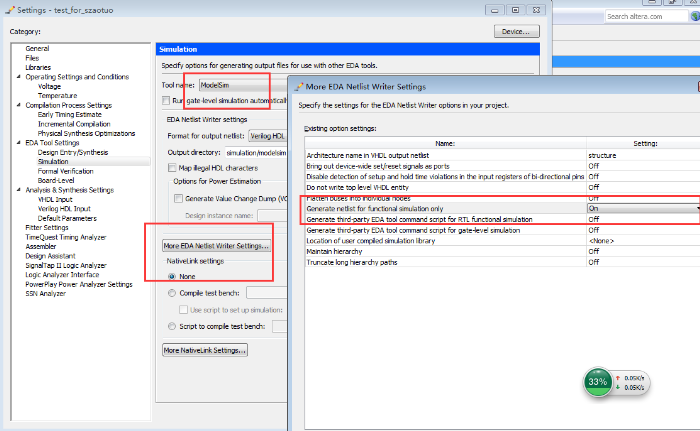

1.关闭modelsim的sim1工程了,建立sim2文件目录,回到quartus

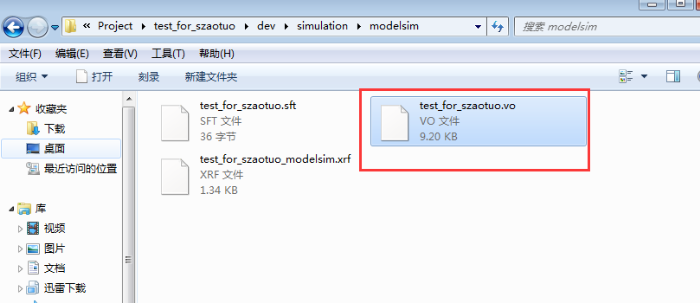

2.然后,点击编译,会在dev目录下产生一个simulation文件夹,找到vo文件

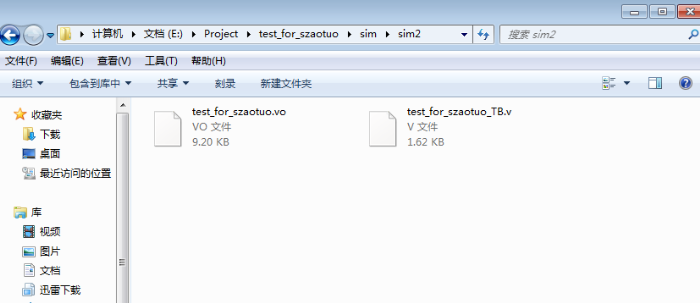

3.建立sim2的modelsim的工程,和上面的类似,但是注意:将vo文件和testbench文件拷贝到sim2文件夹,这一点和上面不同哦。

4.然后和之前不同的是,我们需要添加altera的仿真库,因为不同的器件的门延时不同,网表和器件有关。 |