基于FPGA的应力应变信号监测系统的研究设计(下)

|

- UID

- 871057

- 性别

- 男

|

基于FPGA的应力应变信号监测系统的研究设计(下)

摘要:文中介绍了一种基于FPGA的多通道应力应变信号监测系统的设计方案,该系统的研究为一些大型建筑结构由于年代久远而需要维护、维修提供客观依据,主要阐述了前端信号采集电路硬件以及FPGA上各个控制模块的设计,系统可以通过NiosⅡ软核修改FPGA中的各项采样参数,如采样率、采样通道数、起始通道等,来实现对不同对象的应变情况进行实时监测,模拟实验表明系统运行稳定可靠,采集精度高,具有很高的实用价值。

关键词:FPGA;数据采集;应力应变;NiosⅡ

应力应变是一个物体受力后机构的变化情况,应变就是受力后产生的形变率,通过对应变进行检测,就可以知道物体的受力情况和形变情况。

1 设计思路

本文设计的应力应变检测系统可以实现数据的采集、处理和存储功能。整个系统主要由Altera公司的FPGA芯片CycloneII 2C35F672C6,MAX公司的ADC芯片MAX197,DAC 0832以及信号调理电路等外围电路组成。系统硬件简图如图1所示。NiosⅡ软核输出控制信号,控制FPGA。当NiosⅡ软核启动FPGA开始数据采集后,FPGA通过MAX197控制模块输出通道地址给ADC芯片MAX197,FPCA控制DAC芯片输出模拟量对这一通道的输入量进行粗调零。然后由FPGA控制ADC芯片MAX197进行模数转换。将转换得到的12位数字量输送给FPGA。在FPGA内部将12位数据进行细调零等相应的数据处理,然后加上4位标明通道的数据送入FIFO中。当FIFO达到半满时,NiosⅡ软核将数据读出进行相应的处理,这时候整个数据采集的过程完成,如果数据出现异常,将异常数据通过数据发送单元(DTU)发送至监测中心,系统总体框图如图1所示。

2 信号调理电路的设计

信号调理电路主要由供电电源模块、应变电桥稳压模块、电阻应变桥式电路、前置放大电路、二级放大及滤波电路组成,框图如图2所示。电源模块提供可靠稳定的电压;应变桥式电路作为信号转换电路,把力信号变换成电压信号;前置放大主要由高精度仪用运算放大器AD620为核心,对输入信号进行前置放大并对噪声进行有效抑制,二级放大滤波电路作为后级放大电路同时进行低通滤波,防止高频信号的干扰。

3 A/D转换器的选择及电路连接

A/D转换器是数据采集系统的核心器件,它的技术指标有采样通道数目、输入范同、输入方式、采样率、分辨率、精度、编码宽度等,其中采样率、分辨率、精度是A/D转换器的3个重要指标,直接影响数据采集系统的精度。

3.1 采样率的选择

采样率是指在单位时间内采集系统对模拟信号的采集次数。一个高采样率可以再给定时间下采集更多数据,因此能更好的反映原始信号,但也并不是采样率越高越好,如果采样率太高,当然会得到完美的信号,但同时也会得到大量无用的数据,这将浪费宝贵的存储空间,但如果采样率太低,虽然节省存储空间,将会得到一个无用的采集结果:波形看似正确,实际上是完全错误的。

3.2 分辨率的选择

分辨率是指A/D转换器所能分辨模拟输入信号的最小变化量,它代表了数字值上的最低有效位1(LSB),也称为编码宽度。分辨率是由A/D转换器的位数决定的,位数越大,分辨率就越高,信号范围被分割成的区间数目就越多,输入信号的细分程度就越高,因此能探测到的电压变量就越小,这对于提高像FFT这样的数学分析计算非常重要,但同时也意味着更高的成本。A/D转换器的位数常用的有8位、12位、14位、16位,甚至还有24位的。

过高的分辨率除了成本高,也会带来其他的问题:比如为获得一个稳定的信号,A/D转换需要更多的时间也就是说,分辨率越高,A/D采样越慢。

3.3 精度的选择

精度反映了测量与实际信号值的接近程度,用%来表示,例如,一个具有0.1%系统精度的数据采集系统,测量一个理想的10V的电压源。测量结果带有0.1%的误差,它可能显示高至10.01V或低至9.99V的测量值。显然精度越高,数据质量也就越高,测量结果也就越加可信。

综合上面几个因素考虑,本系统的A/D转换器选用MAX197,MAX197芯片是美国MAXIM公司近年的新产品,是多量程(±10V,±5V,0~10V,0~5V)、8通道、12位高精度的A/D转换器。它采用逐次逼近工作方式,有标准的微机接口。三态数据I/O口用做8位数据总线,数据总线的时序与绝大多数通用的微处理器兼容。全部逻辑输入和输出与TTL/CMOS电平兼容。新型A/D转换器芯片MAX197与一般A/D转换器芯片相比,具有极好的性价比,仅需单一+5V供电,且外围电路简单,可简化电路设计。

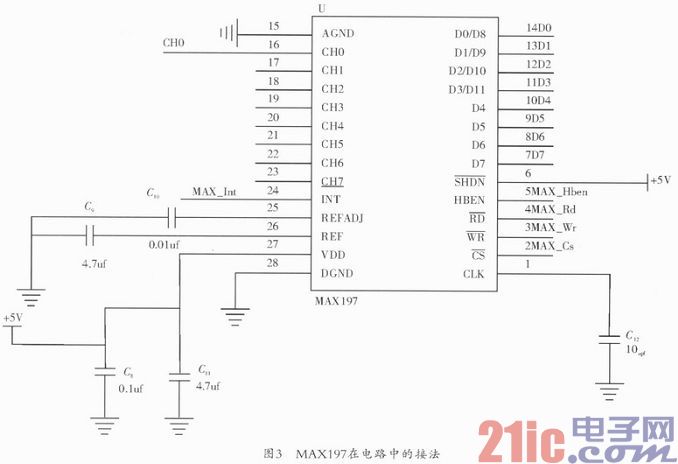

MAX197工作时,参考电压可以由片内提供或片外输入,视实际需要而定,当使用片内参考电压时,可在REFADJ端和REF端分别获得精度为±1.5%的参考电压2.5V和4.096V。当使用外部参考电压时,参考电压可以分为从REF或REFADJ输入当从REF输入时,只要把REFADJ和VDD相连,并在输入端REF和地之间加接一个4.7μF旁路电容;当从REFADJ输入时,只要REF端通过4.7μF电容旁路到地,并在输入端与地之间接一个0.01μF旁路电容,这种输入方式可以省掉外接缓冲放大器,MAX197的电路接法如图3所示。

4 基于FPGA的控制模块的设计:

本设计利用SOPC技术存FPGA内部集成Nios II嵌入式处理器作为控制模块,可以像单片机一样用C语言对其进行编程开发,易于实现复杂功能,而且使用Nios II开发时可以根据实际情况选择所需的PIO和外设数量,定制出所需的系统,避免资源浪费,降低系统功耗。

4.1 Nios II软核的搭建

首先需要添加的是CPU,NiosII软核为用户提供了三种具有不同功能的CPU配置。本系统选择Nios II/f类型,对系统所需CPU的性能和逻辑资源的占用率进行了平衡。

4.2 建立锁相环PLL模块

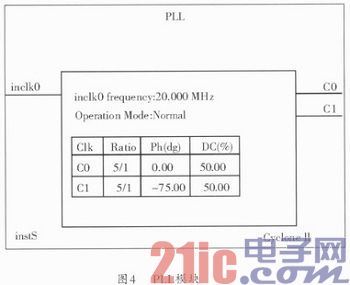

搭建好软核之后还需要建立一个锁相环,对时钟进行倍频.由于前期所用的开发板上是20MHz的有源品振,需要将其倍频到100MHz以满足之前搭建的软核的时钟,还需要为SDRAM提供100MHz的时钟,在Quartus II9.0中用HDL语言设计生成的A/D控制模块如图4所示。

|

|

|

|

|

|