1概述

当今计算机系统DDR3存储器技术已得到广泛应用,数据传输率一再被提升,现已高达1866Mbps.在这种高速总线条件下,要保证数据传输质量的可靠性和满足并行总线的时序要求,对设计实现提出了极大的挑战。

本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。

2 DDR3介绍

DDR3内存与DDR2内存相似包含控制器和存储器2个部分,都采用源同步时序,即选通信号(时钟)不是独立的时钟源发送,而是由驱动芯片发送。它比DR2有更高的数据传输率,最高可达1866Mbps;DDR3还采用8位预取技术,明显提高了存储带宽;其工作电压为1.5V,保证相同频率下功耗更低。

DDR3接口设计实现比较困难,它采取了特有的Fly-by拓扑结构,用“Write leveling”技术来控制器件内部偏移时序等有效措施。虽然在保证设计实现和信号的完整性起到一定作用,但要实现高频率高带宽的存储系统还不全面,需要进行仿真分析才能保证设计实现和信号质量的完整性。

3仿真分析

对DDR3进行仿真分析是以结合项目进行具体说明:选用PowerPC 64位双核CPU模块,该模块采用Micron公司的MT41J256M16HA—125IT为存储器。Freescale公司P5020为处理器进行分析,模块配置内存总线数据传输率为1333MT/s,仿真频率为666MHz.

3.1仿真前准备

在分析前需根据DDR3的阻抗与印制板厂商沟通确认其PCB的叠层结构。在高速传输中确保传输线性能良好的关键是特性阻抗连续,确定高速PCB信号线的阻抗控制在一定的范围内,使印制板成为“可控阻抗板”,这是仿真分析的基础。DDR3总线单线阻抗为50Ω,差分线阻抗为100Ω。

设置分析网络终端的电压值;对分析的器件包括无源器件分配模型;确定器件类属性;确保器件引脚属性(输入\输出、电源\地等)……

3.2电路前仿真分析

前仿真分析的内容主要是在PCB设计之前对电路设计的优化包括降低信号反射、过冲,确定匹配电阻的大小、走线阻抗等,通过对无源器件的各种配置分析选取出最适合的参数配置。

图1时钟线的拓扑结构(点击查看大图)

(1)DDR3总线的差分时钟分析

众所周知,在差分传输中,所有信息都是由差模信号来传送的,而共模信号会辐射能量并能显著增加EMI,因此保证差分信号的质量十分重要,应使共模信号的产生降到最低。在对差分时钟分析时不仅要关注其本身的信号质量,由于其它信号都是以差分时钟的来采样数据,因此还需关注其单调性、过冲值等。

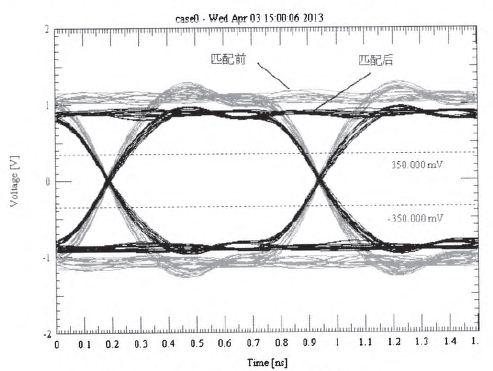

本例中差分时钟的fly—by拓扑结构与地址总线一样为串联方式,如图l对处理器P5020驱动4个DDR3内存芯片的时钟拓扑结构,在终端进行简单的电阻匹配,在PCB板上差分走线后,进行反射分析发现接收端反射波形上下过冲较大。在处理器输出端选用正确的下拉匹配电阻,虽电压幅值略有减少,但上下过冲明显减少消除了反射干扰,即减少了差分线的共模分量。对比分析结果如图2.

图2接收端DDR3的反射波形

(2)验证驱动能力和ODT选项

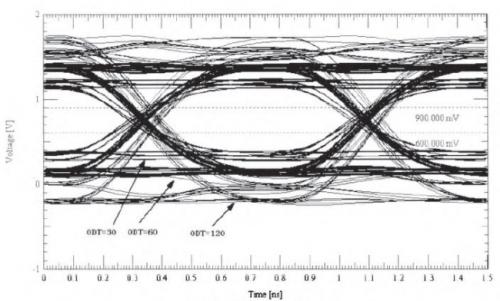

DDR3内存总线数据信号的驱动能力分为FULL和HALF两种模式,内部终端电阻(ODT)选择也有0Ω、20Ω、30Ω、40Ω、60Ω、120Ω选项,它们分别对应不同的模型用于控制信号反射的影响。为提高信号质量、降低功耗,可通过分析不同模式选取正确的参数模型。

取数据总线对不同的ODT选项进行分析。图3是在不同ODT设置进行分析数据信号形成的眼图波形,从图中可以看出:ODT阻抗越高,在相同驱动激励和走线等情况下转换率越高,幅度越大;在选择ODT=60Ω,其接收波形平缓信号质量最好,无明显抖动和过冲,抖动最小。

图3数据信号眼图波形

通常串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声干扰。它生成前向串扰与后向串扰,其对信号波形主要影响在幅度和边沿上面。

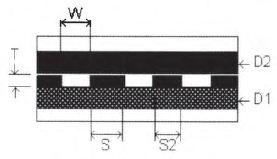

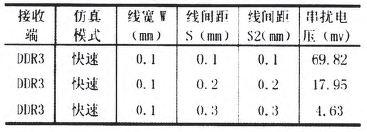

从DDR3数据总线提取3根相邻线,中间一根为被攻击网络,周围2根为攻击网络,采用3线模型进行分析,如下图4走线排列,其受害线为中间走线保持低电平,两边的为攻击线,采用128位伪随机码,根据走线的不同线宽和线间距对其进行串扰分析,看其分析结果如下表1.

图4走线剖面图

表1串扰分析结果

从表1可看出间距越大串扰影响越小,这里我们遵循的3W原则即走线边沿间距S是线宽W的3倍将大大减少串扰的影响。但间距增大将牺牲布线空间,因此需综合考虑使在有限的空间中布线最优化。 |