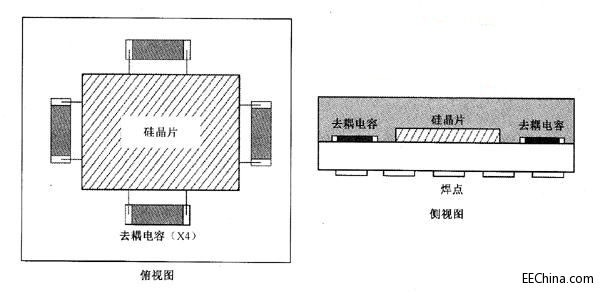

现代微处理器、数字信号处理器和专用集成电路等技术的飞速发展,已成为电磁干扰的主要来源。如今 的主要辐射源不再是由不合理的步线、板结构、阻抗失配或电源不稳定原因所产生。器件的工作频率已从 20~50 MHz发展到了200~5000 MHz,甚至更高。随着时钟频率的提升,每个VLSI器件存在切换电流,切 换电流的傅里叶频谱产生RF能量,使得数字器件必然会存在辐射。 现代集成电路工艺的发展使得上百万的晶体管被集成到一块小硅片上,生产工艺达到了0.18 μm线宽 。虽然硅片尺寸不断收缩,但元件数量增加了,使得产品的批量生产、降低制造成本成为可能。同时,线 宽越小,两个逻辑门元件之间的传输延时就越短。但边沿速率加快,辐射能力也就随之增强,状态切换效 应在集成芯片内部之间感应的作用下,加大了能量损耗。 硅片需要从电源分配网络中获得电流,只有当电流达到一定数值时才能驱动传输线。边沿速率越快,就 需要提供达到更快速率的直流电流。切换开关在电源分配网络中的来回转换,会在电源板和接地板之间引 起差模电流的不平衡。随着共模、差模电流的失调,在EMI测试中,会发现共模电流在电缆组装连接处或 PCB元件中产生辐射。 元器件供应商可以采用不同的技术把去耦电容嵌入到集成芯片当中。一种方法是把硅晶片放到集成芯片 之前先嵌入去耦电容,如图1所示。

图1 硅芯片封装内部的去耦电容

双层金属膜中间再加一层介质层,就形成了一个质量可靠的平板电容器。由于外加电压很低,所以介质 层可以做得很薄。对于一个很小的区域,它产生的电容完全可以满足需要,并且有效的引线长度趋于零。 另外,平行板结构获得的谐振频率非常高。这种技术的优势突出在成本很低,在不需要分立去耦电容的情 况下可以提高性能。 另外一种方法是在集成芯片中来用强压技术形成去耦。高密度元件常常直接把表面安装(SMT)电容加 入到集成芯片之中。分立电容常在这个时候用于多芯片模块中。根据硅盘入侵峰值电流冲激情况,以设各 所需的充电电流为基础来选择合适的电容。此外,在元件产生自激时能对差模电流产生抑制作用。如图2所示,虽然内嵌有电容,在模块外部同样需要加上分立电容。 正如前面所述,元件在开关周期内,去耦电容提供了瞬时的充、放电。去耦电容必须向器件提供足够快 的充、放电过程以满足开关操作的需要电容的自激频率取决于很多因素,不仅包括电容大小,还包括ESL、ESR等。

图2 多芯片模块内部的去耦电容布局

对于高速同步设计而言,CMOS功率损耗表现为容性放电效应。例如,—个在3.8 V哇压、200MHz频率下的设备损耗4800 mW的功率时,就会大约有4000 pF的容性损耗。这可以在每个时钟触发下观测得到。 CMOS逻辑门通过自身的输入电容,对设备的耦合和输入晶体的串联电容来提供分有电容。这些内部电容并不等于运行所需的电容值。硅盘不允许使用另外的硅材料制作大眭容底板,这是因为制造工艺决定了亚微米设计会消耗布线空间,同时需要支持氧化物层献装配。 |