|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

引言

使用低侧栅极驱动器驱动MOSFET在照明、功率转换、电磁阀驱动、电机控制和其他负载应用的地电压不稳的系统中很常见。栅极驱动器能设计为可提供能高效驱动所需的高峰值电流。许多HVIC(高电压IC)设备用来驱动半桥拓扑应用,因此包括一个低侧栅极驱动器。为大多数应用设计并选择低端栅极驱动器很简单,只需基本了解驱动它们所需的功率MOSFET管的基本特征和驱动所需信号即可。尽管照明和阻性发热等阻性负载可能在应用中占少数,但为简洁性本文以驱动纯阻性负载为列来做说明。

MOSFET的栅极电荷基本特性

MOSFET的栅极电荷参数反映了正常工作时区域的工作状况。飞兆AN-7502功率MOSFET开关波形深入解释了MOSFET在不同应用中相对应的不同区域。

在选择合适大小的栅极驱动器时,与输出电流能力的相关的MOSFET参数主要包括:

Qg(th) – 达到阈值电压所需的栅极电荷

Qgs2 – 从阈值电压到平台电压所需的栅极电荷

Qg(tot) – 达到彻底“导通”电压的总栅极电荷

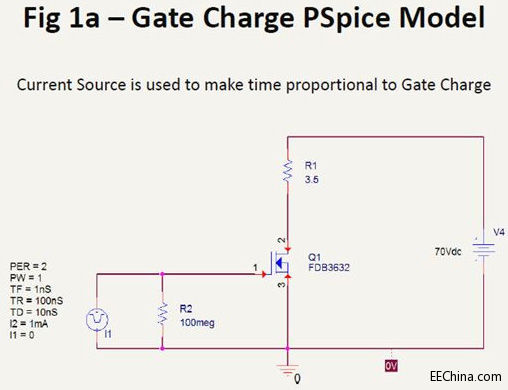

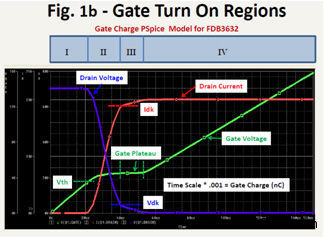

在图1a中,Pspice模型中的1mA恒流源用于帮助创建带阻性负载时导通期间典型栅极波形(图1b)的曲线。栅极电荷与显示的时间轴成正比,比例系数为0.001。可为良好建模的任何MOSFET轻松创建类似设备特定的曲线。

2013-11-22 10:44:32 上传 2013-11-22 10:44:32 上传

下载附件 (25.44 KB)

2013-11-22 10:44:32 上传 2013-11-22 10:44:32 上传

下载附件 (23.38 KB)

在区域I中,栅极电压上升至Vth(栅极阈值电压),然后MOSFET开始导通。区域I结束时的栅极电荷为Qg(th)。

在区域II中,栅极电压上升至平台区,漏极电压达到Vdk(漏极膝点电压)标志来到这一区域,同时漏极电流的上升斜率(dI/dt)显著减小。在区域II中,不仅栅极驱动电路驱动栅极,而且源极电感和漏极至栅极的电容提供负反馈影响栅极的驱动。源极电感主要由MOSFET的绑定线(bond wires)和封装引脚构成。实际使用中,此区域可能表现为高速振铃。新的无引线MOSFET封装往往具有更低的寄生电感,因此自电流快速变化带来的影响也更小。区域II结束时的栅极电荷为Qg(th) + Qgs2。

在区域III或称栅极平台区(米勒平台)域中,漏极的dV/dt减小。漏极电流的dI/dt也相应减小。注意电压和电流波形中的膝点Vdk和Idk。在区域III中,栅极电荷增加,但栅极电压几乎不变,直到器件达到完全导通状态。区域III结束时的栅极电荷通常不由制造商标出。

在区域IV中,也就是在栅极平台区后,增大栅极电压将继续降低导通电阻Rds(漏极至源极电阻)。在特定栅极电压和环境温度下达到已知Rds点所需的栅极电荷标为Qg(tot)。对于标准栅极器件来说,这通常为10V,而对于逻辑电平器件来说,为4.5至5V。用于特定低电压开关应用中具有较低阈值的MOSFET的栅极电压则有所不同。

如Rds(漏极至源极电阻) 和Vth (栅极阈值电压)等MOSFET的参数将随温度而变化,这在大多数设计中都很重要。但是,栅极电荷参数不那么依赖半导体工艺处理,而更多地与裸片几何尺寸相关,因此具有最小的温度变化影响。

初始设计考量

通常,设计人员需要先确定最小栅极驱动输出要求。栅极驱动电路必须能够在一段既定的时间内提供所需的Qg(tot)。其次,必须减少区域II和III上的转换时间以最大程度地减少开关损耗。

栅极驱动器标出了多个参数,以帮助设计人员根据这些要求确定驱动器的大小。在固定容性负载下,吸入Isink和输出Isource电流能力在对应Vdd/2或中值电压点时标出。同样标有上升和下降时间。在某些情况下,负载特性可能需要不同的导通和关断能力。尽管MOSFET的Vth通常比用于驱动栅极的Vdd小,栅极Rg上的电压在关断期间的栅极平台区较低。因此, 许多低侧栅极驱动器为比高侧驱动器设计得有更强的的电流能力来补偿Rg上电压的降低带来的影响。

额定电流值是栅极驱动器选择中的主要参数。实际上,栅极驱动器系列通常用额定电流值来区分。飞兆提供1、2、4和9A的低电压系列。

第二重要的因素包括在多通道器件中的传导延迟,传导匹配栅极驱动器的输出驱动能力也受到裸片和封装的总热耗散能力搜限制,同时也受到开关频率的影响。

在第2部分中,我们将探讨最常见的低电压栅极驱动器电路和一些其他设计小技巧。 |

|