基于Visual DSP++4.0开发的TigerSHARC DSP多处理器系统及其应用 (2)

|

- UID

- 1029342

- 性别

- 男

|

基于Visual DSP++4.0开发的TigerSHARC DSP多处理器系统及其应用 (2)

1.3外部存储器

ADSP-TS201S片内的24Mbit嵌入式DRAM (e-DRAM)既可以存放程序,也可以存放数据。然而,在某些应用中,也需要使用外部存储器。外部存储器可在MP系统中作为系统中所有DSP的共享资源,也可以由某个处理器专用。

在硬件系统中使用不同类型的存储器时,系统中所有的DSP都必须建立对它恰当的访问方式。用户可通过系统控制寄存器(SYSCON)来对访问方式进行编程。用户定义的设置必须支持与存储器设备相一致的访问模式,而该访问模式正是用户希望在硬件系统中使用的访问方式。共享外部总线簇连接的所有处理器的SYSCON寄存器都必须有相同的设置。 ADSP-TS201S支持对SDRAM的无缝连接。和SYSCON寄存器一样,所有处理器的SDRAM配置寄存器(SDRCON)也必须设置成相同的值。DSP的内部存储器控制器一旦配置,DSP就可以通过外部总线访问外部存储器。

笔者设计的本系统有两个DSP,并将SDRAM作为它们的外部共享资源。下面是其程序代码,从该代码可见,其与SDRCON寄存器的初始化相一致。

其中Shared.asm文件中包含了一些变量定义,这些变量就是放置在外部存储器中的数据。实际上,本系统中有最小ID号的DSP(也是系统中优先权最高的)在加载过程中,负责初始化在.ASM共享存储器文件中定义的外部数据变量。

1.4矢量中断(VIRPT)

矢量中断用于主机和DSP之间,或者DSP和DSP之间的通信。该中断是其它主处理器使用的通用中断。通过把中断子程序的地址写入VIRPT寄存器,主机或主DSP就可以从DSP发出矢量中断命令。当服务该中断时,高优先级中断将使DSP转到子程序地址,以服务该子程序。

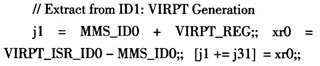

上例中,通过把ID0中服务子程序地址写到ID0中的VIRPT寄存器(0x11807300=0x1807300VIRPT地址+0x10000000 MMS ID0)中,可使ID1触发ID0的矢量中断。

一旦外部定义的标号用作ISR地址(如例中的VIRPT_ISR_ID0),服务中断(MMS_ID0)的DSP的MMS偏移量就必须减去某个值,才能正确的对应到ISR的矢量地址。

上例仅仅说明了如何使用内部处理器的VIRPT中断作为标志,或者表征MP系统中程序已经执行完成。

2 多处理器的数据传输

多处理器系统往往需要进行海量数据流的处理,以提高系统的工作效率。通常用于实现ID0和ID1之间的直接存储器(DMA)、从ID0和ID1到外部存储器(SDRAM)、从ID1到ID0的核传输、对系统中所有DSP广播式写操作等几种外部端口(EP)的数据传输。

TigerSHARC包含了14个DMA通道,其中4个指定为外部存储器设备(通道0、1、2、3)。

2.1 从ID0到ID1的DMA传输

本实例说明了从ID0内部存储器到ID1外部存储器的DMA数据传输。在这种情况下,DMA通道0可将tx_ID0中存储的数据传输到rx_ID1中。但这种传输方式必须建立两个传输控制块(TCBs),其中一个是源地址,另一个是目的地址。

由于在该实例中没有选择2维DMA,因此,应注意寄存器xr2和yr2中的值是不相关的。只要源和目的TCB装入新值,DMA传输就会开始。一旦DMA完成,就产生中断,并运行_dma_int矢量中断程序。

下面是用DMA通道0将值载入到每个TCB的程序代码:

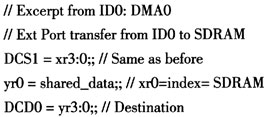

2.2 ID0到SDRAM的DMA传输

从ID0内部存储器到SDRAM进行数据传输时,只需对以前的例子作细微的改动即可。即先使源TCB装人的值和前面(xR3:0)寄存器的值相同,目的TCB则用寄存器yr3:0的值写入,而yr0的值则由rx_ID1改变为shared_data。这种情况下,就可通过DCS0和DCD0分别代替DCS1和DCD1,并用DMA通道1实现数据传输。代码如下:

|

|

|

|

|

|