基于ADSP-BF5619处理的H.264视频编码器设计

|

- UID

- 1023166

- 性别

- 男

- 来自

- 燕山大学

|

基于ADSP-BF5619处理的H.264视频编码器设计

1 引言

H.264/AVC是ITU-TVCEG和ISO/IEC MPEG联合制定的最新视频编码国际标准,是目前图像通信研究领域的热点问题之一。H.264的视频编码层(VCL)采用了许多新技术,因而使得编码性能大幅度提高。与以往的视频编解码标准相比,在相同的码率下,H.264具有更佳的图像质量,这使得H.264在无线通信和网络传输等低码率视频应用领域得到了更为广泛的应用。但这是以复杂度的成本增加为代价的,故使H.264在实时视频编码及传输应用中面临巨大的挑战。而用高性能数字信号处理器(DSP)来实现H.264实时编码器是一种快速有效的方法,有助于H.264视频标准的迅速推广和应用。

ADSP-BF561处理器性能卓越,具有600 MHz的主频,且集成了一套通用的数字图像处理外围设备接口,从而为多媒体和图像应用创建了一个完美的系统级片上解决方案。本文针对低码率视频传输的需要,研究并实现基于H.264标准的视频编码系统,同时探讨H.264软件编码器在DSP上的实现及优化方法。

2 H.264编码算法及ADSP-BF561简介

在实际开发过程中,针对H.264的算法特点和ADSP-BF561双核处理器的结构特性,本文做了大量优化工作,从而在保证编码精度的同时,大幅度提高了编码速度。下面简要介绍H.264视频编码算法和ADSP-BF561双核处理器系统。

2.1 H.264编码算法

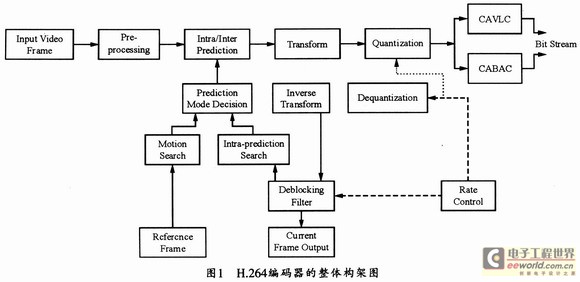

H.264是ISO和ITU联合制定的新一代视频编码标准,具有很高的压缩比和很好的鲁棒性。其整体框架如图1所示。

在继承了原有视频编码标准的基础上,H.264作了多方面的改进,包括引入4×4子块和16x16子块共9种模式的帧内预测。帧内模式的引入是为了与变换编码一起用于消除空间上的冗余,进而大大提高编码效率。在帧间模式中,H.264可支持多尺寸的运动估计和补偿。其帧间预测时块的大小不是固定的8x8,而是可以从4×4到16x16,并且包括长宽不等的块(共7种类型),同时支持多参考帧,故可大大提高预测性能。此外,H.264还采用整数DCT变换来降低计算量,同时采用自适应算术编码来提高编码效率,并可利用滤波器消除低比特量化带来的块效应等。事实上,H.264的效率比现有的编码技术可提高50%。

2.2 ADSP-BF561芯片结构

ADSP-BF561是一种双核750 MHz处理器,具有对称多处理(SMP)系统结构。其SMP结构在信号处理和控制功能的集成和分割方面能够为用户提供较高的性能和较大的设计灵活性。ADSP-BF561的系统结构如图2所示,它包含coreA和coreB两个核,每个核的处理频率可达750MHz。两个核都有各自独立的32KB L1指令存储器(16KB Cache/SRAM)和64KB L1数据存储器(32KB Cache/SDRAM),并可共享128KB L2存储器。两内核访问不同内存时,其速率有明显差异,其中访问L1存储器最快,L2次之,而访问片外内存和设备则最慢。

由于访问存储器速率的差异。双核之间进行数据交换最好在L1段直接进行,而且需要使用IMDMA控制器。这个DMA控制器的主要功能是在双核之间的L1存储器之间进行数据交换。使用IMDMA控制器可以在访问速率比较慢的片外内存或者对L2进行数据处理操作时,提高数据处理的速率,进而提高编码效率。

3 H.264视频编码算法的优化与实现

对编码器的优化主要是对P帧编码流程的优化和对ADSP-BF561双核处理系统的优化,合理的流程有利于各种模块的独立性和完整性,同时有利于以后只针对某个模块的优化或升级处理。而利用ADSP-BF561的双核协调处理优势可以进一步提高其速度。

3.1 P帧编码流程的优化

由于H.264编码算法比较庞大,对程序细节上进行优化事实上不能带来明显的效率提高,所以应对程序流程本身进行调整。在H.264编码器JM86版本中,I帧、P帧的编码采用同一模块,这样就有大量帧内、帧间宏块的重复判断,故使编码速度受限。

Micro_h264编码软件模型针对这一缺点进行了处理,将I帧、P帧的编码提取出来分别独立编码。但是遗憾的是,micro_h264编码软件模型对一帧图像的宏块进行编码是按照宏块在图像中的光栅扫描顺序一一进行的,没有考虑到宏块在一帧图像中的不同位置有着不同的特性,而且对这些宏块采用统一模式进行编码,也会产生很多判断条件,这不但不利于DSP的流水操作,也不利于模块的优化。本文针对这一个缺点对micro h264的P帧编码流程进行优化。

根据宏块在一帧图像中位置的不同,可以对不同位置的宏块分别独立进行编码。同时,根据子块在宏块中的不同位置,也可以对其进行独立编码。

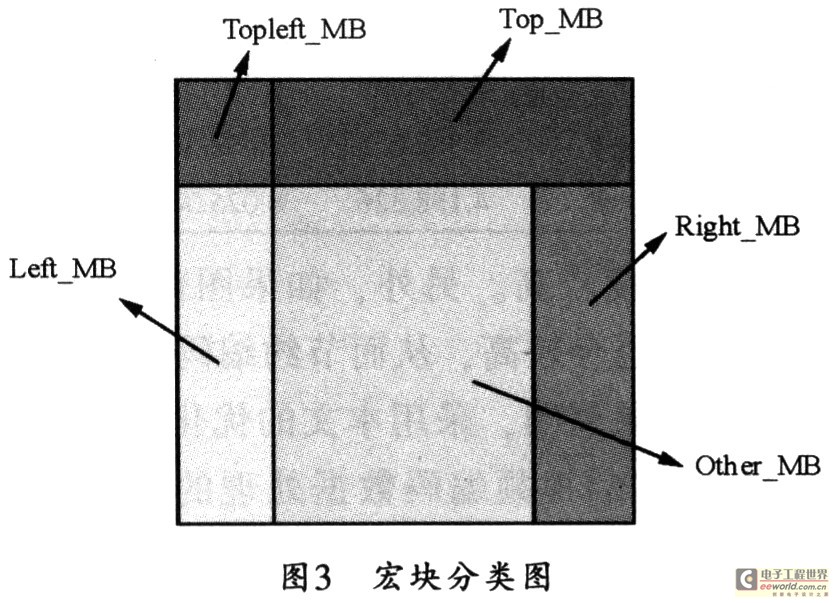

一帧图像被分成多个宏块时,不同位置的宏块有不同的特性。因此,可以根据宏块在一帧图像中的不同位置来对宏块进行分类,以将具有相同编码特性的宏块归为一类,这样,可以将帧图像的宏块分成五类。图3所示是其宏块分类图。

通过对宏块进行分类,可对不同的宏块调用不同的函数来对其独立编码,从而减少很多不必要的判断,这样就不会打断DSP的流水操作,达到提高速度之目的,同时在进行优化时也更具针对性。

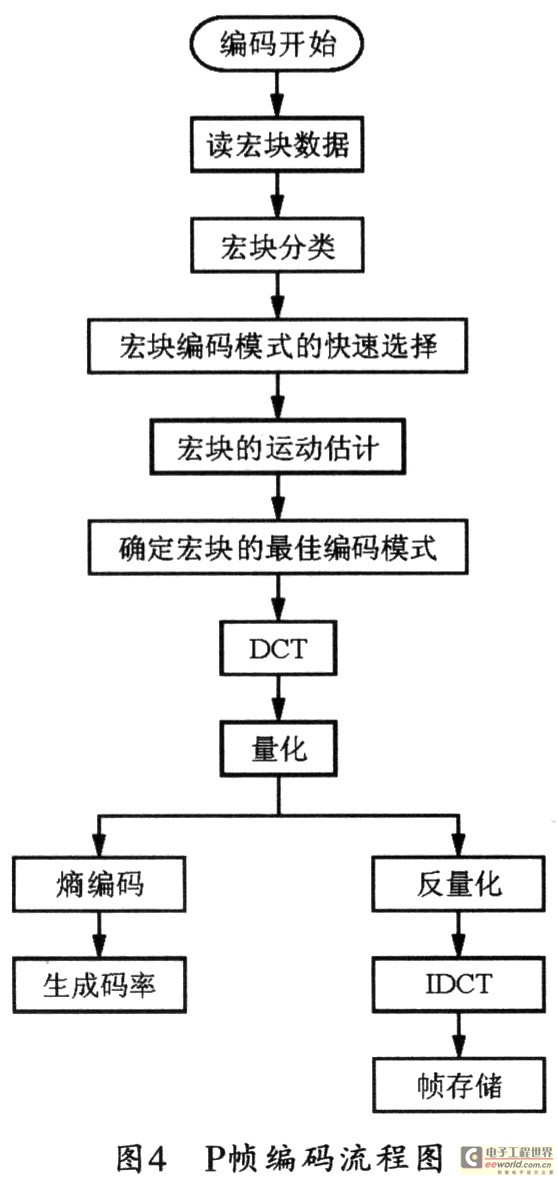

本编码器在P帧编码时,只用了一帧参考帧,并且改进了micro_h264编码器软件模型所使用的对宏块编码模式逐一遍历的算法,而是采用宏块编码模式快速选择算法。P帧编码的流程图如图4所示。

运行平台的不同,软件结构也应该根据各自的特点做些调整。较低复杂度的编码器可将多个不同类宏块独立出来单独处理,这样可以省去许多中间的重复判断,不仅能提高编码速度,同时程序结构也显得更为清晰,而且,由于各个模块的相对独立,也有利于程序的扩展。虽然这样在一定程度上增加了代码量,但却能有效地提高编码速度。

3.2 ADSP-BF561双核处理系统的优化

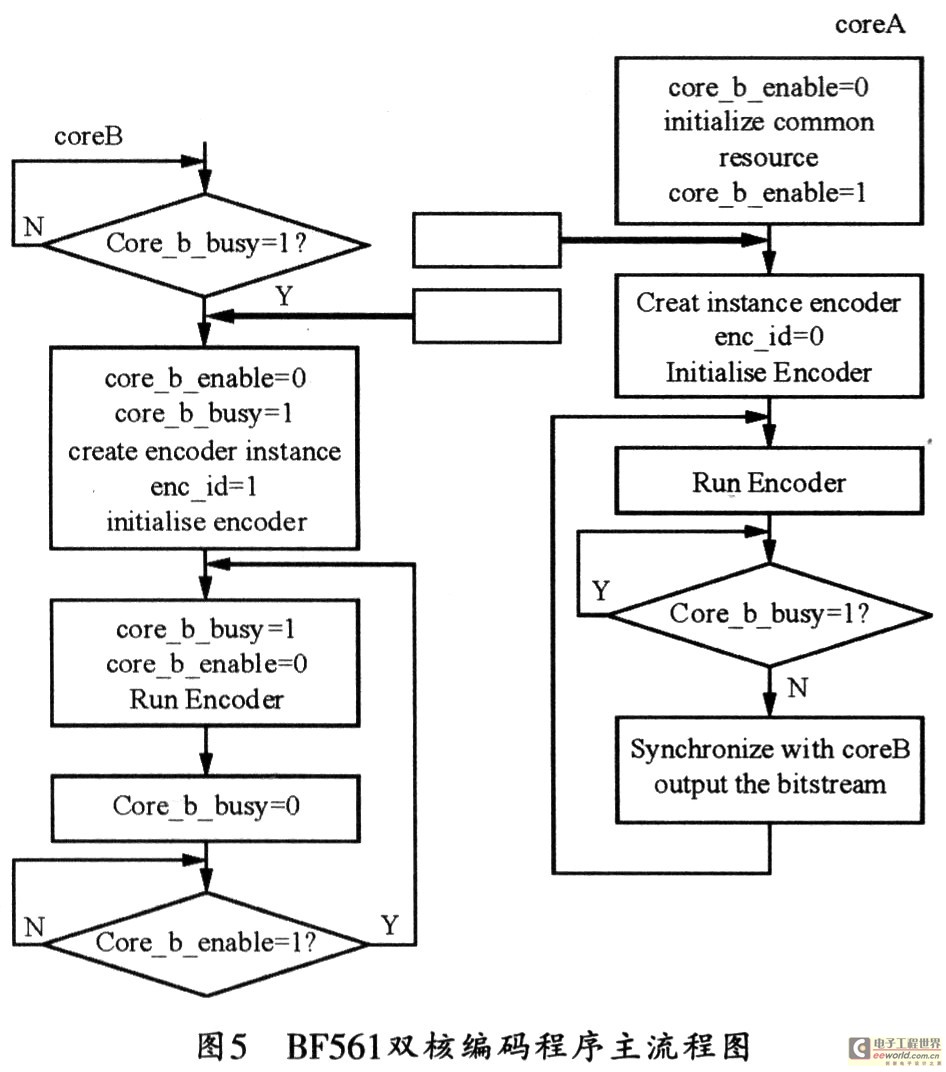

为了保证编码器的稳定工作,本文把内核定位在600 MHz,如果能在600 MHz的基础上实现4CIF格式的实时编码,那么,提高内核处理频率就能支持更高质量的4CIF格式的视频编码处理。为了实现25帧图像的实时编码,每帧需要的时钟周期数为600 MHz/25=24MHz,即需要在24 MHz时钟周期数内编码一帧。大约相当于在6 MHz内进行一帧CIF格式的视频处理,显然,如果使用一个核是很难做到实时编码处理的。本文不同于大多数双核系统的一个核运行操作系统,而另一个核运行其它软件的工作方式,是将编码器放在两个核内同时进行处理。

在ADSP-BF561开发板上实现这个编码算法时,其主要的难点是两个核之间如何通信以及协调工作。双核同时运行一个视频编码程序时,需要对数据进行共享和交换。虽然,使用片外内存或者L2共享存储器来进行宏块数据交换的实现方法比较简单,且不需要进行数据的拷贝,但是,大量访问低速率存储器的操作将极大地影响程序执行的速率,进而影响编码器的编码效率,所以,不能采用共享内存来进行宏块数据的交换。本文采用的是IMDMA在双核各自的L1数据段直接进行数据交换,而且在编码处理的同时进行内存数据的交换,从而避免了大量访问低速率的存储空间操作,减少了程序执行的时间。而由于消息交换数据量很小,可以使用共享存储器,因此,可以采用访问速率相对较快的L2存储器来进行存取。事实上,笔者已经经过优化编程在BF561开发板上实现了上述编码算法。其双核编码主流程如图5所示。

4 试验结果与数据分析

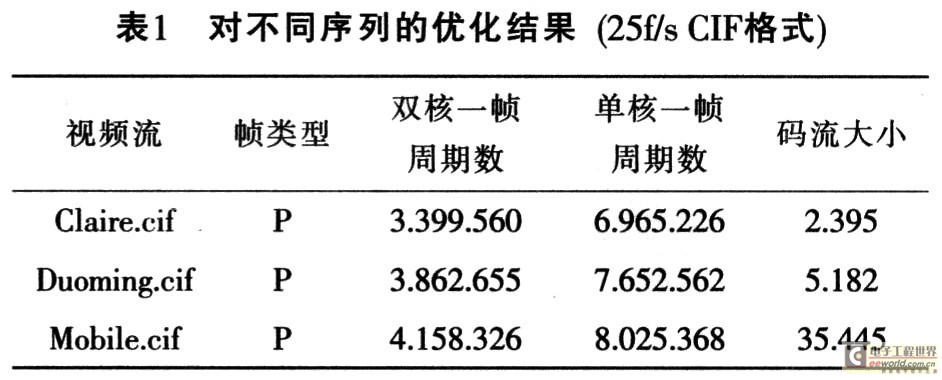

经过优化,H.264的编码性能有了较大的提升,实现了在BF561芯片上对4CIF格式视频的实时编码处理。同时,笔者还在VisualDSP++5.0编译环境下分别对原编码器和双核编码器实现的编码结果进行了测试,其结果如表1所列。事实上,编码速度基本取决于图像画面的运动情况和颜色是否丰富。从上面的数据可以看出,对于不同序列,其编码速度也不同。Claire序列的编码速度之所以很快,是因为图像背景静止,只有肩部和头部有运动,所以编码数据量较表1对不同序列的优化结果(25f/s CIF格式)少,编码速度较高。另外,如果图像比较简单,其编码速度也会较高,从而节约编码时间。

试验结果表明,采用本文的优化方法可以节约大量的H.264视频编码数据处理的时间,能较好地满足4CIF视频序列实时编码的要求。而对于很复杂的图像,也可以在一定的量化参数下实现4CIF的实时编码。

5 结束语

本文重点研究了基于ADSP-BF561双核处理器的H.264视频编码算法的优化及其实现方法。同时针对ADSP-BF561双核处理器的体系结构,对编码的关键部分进行了算法流程的调整,并通过BF561双核之间的数据交换和协调工作,在双核上实现了4CIF格式视频数据的实时编码。实践证明,使用VisualDSP++5.0仿真软件,在ADSP-BF561开发板上实现25f/s的H.264 4CIF视频编码系统,可以满足人们对视频传输的需求。 |

|

|

|

|

|