QPSK数字调制解调的FPGA实现,包括源程序(2)

|

- UID

- 1029342

- 性别

- 男

|

QPSK数字调制解调的FPGA实现,包括源程序(2)

3.QPSK调制的FPGA实现

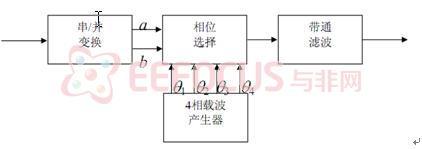

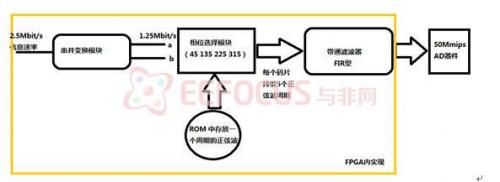

QPSK的FPGA设计内部逻辑关系如下图2所示,设计最高发送信息速率为2.5Mbit/s,首先经过一个串并变换模块将信息速率减半至1.25Mbit/s,然后经过相位选择模块分别选择45 135 225 315度相角中的一个作为正弦波的初始相位,每个码片持续5个正弦波周期,由于在每个码片的开始和结束会跟其相邻的码片的相位存在差异,导致输出的信号频谱发生严重的混跌,不便于后续处理,所以在输出端口加入FIR型带通滤波器,让带外信号尽快的衰减至最小。

输出的信号经过AD变换,转换成模拟信号,此时的信号可以输出到后续相关芯片进行处理,本文不再做介绍。

图2 系统框图

调制代码文件之间的逻辑关系入下图所示:

各个文件的逻辑关系

其中QPSK_CODING.V文件是调制的最上层文件,其对外端口如下所示,

module QPSK_CODING(clk_2_5M,clk_50M,clk_1_25M,EN,din,ready,dataout,count);

input clk_2_5M,clk_50M,clk_1_25M,EN,din;

output ready;

output [15:0]dataout;

output [5:0]count;

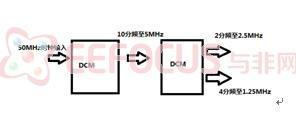

本设计用到3种时钟,他们之间的关系如下所示,时钟在具体的硬件实现是要有2个DCM单元组成。  数字时钟管理单元

各时钟之间的关系图

下图所作的仿真是假设有14bit的数据输入到改调制模块,最后经过调制器后的输出结果如下所示:

经过调制后的QPSK信号波形图(未加滤波器前的输出)

改设计的其他相关模块的设计上层逻辑模块如下所示:

数据经过串并变换模块module serial_to_parallel(clk_2_5M,EN,din,ready,dataout);

然后再经过产生正弦波模块module Produce_Sin(EN,clk_2_5M,clk_50M,datain,ready,addr,count); |

|

|

|

|

|