|

- UID

- 1023230

|

电子产品越来越轻薄短小,电子零件的集积度也就越来越高,而电源、接地噪声(Noise)与讯号(Signal)及其彼此间的耦合(Coupling)现 象,也变成了电子产品在设计时,主要而必须克服的关键因素。

而这些无论是来自于系统外部,或是来自于系统本身的噪声或讯号,对讯号间的辐射 (Radiation)或传导(Conduction)干扰问题,若在30MHz到1GHz的频率范围,就是所谓的电磁干扰(EMI, Electromagnetic Interference)问题;当影响到了更高频的无线传播频率区段(RF, Radio Frequency)时,则又称为无线频段干扰(RFI, Radio Frequency Interference)的问题。而在可携式产品中,RFI的问题更严重影响到了产品的通讯质量。

要解决这些烦人的电磁干扰问题,首先从大的方向来分类,可分为讯号完整性(SI, Signal Integrity)的问题,以及电源完整性(PI, Power Integrity)的问题。在实务的量测解析上,会使用到近场(Near Field)量测的除错模式(Debug Mode),及远场(Far Field)量测的验证模式。如果对于产品的组件特性及边界条件掌握度够高,也可以用仿真软件(如ANSYS、Keysight、CST...等公司所提 供的电磁模拟工具)来做模拟验证与预测。若要对产品中各组件在各种运作下的特性进一步了解,还会使用时频(Time-Frequency)的数值分析方法 (如FFT, HHT, enhance-Morlet Transfer...等)。在产品的设计实务上,要解决这些问题的手法,不外乎必需使用到滤波(Filter)、移频(Moving Resonant Frequency)、展频(SSC, Spread Spectrum Clock)...等手法。

展频的手法,在现今的科技多已做入了集成电路(IC, Integrated Circuit)中,大多与频率相关的集成电路都会有展频的设计,主要用在解决讯号在线的主频能量太强之问题。移频则是一种较笼统的解决方案之说法,主要 目的是把有问题的频率极点位置,移开出目前所在意的频段范围。但是如何找到问题率频点,大多只能仰赖仿真工具来找出频率响应(Resonant)点,才能 再想对策(如加滤波组件或改变线宽、线长或方向)来重新布局。但是,由前面所提及的解析注意要项中可知,如果对组件特性及边界条件不够完整的情形下,非常 容易变成了GIGO(Garbage In Garbage Out)的结果。而使用滤波器则是最为直观且直接的解决手法,当然其中也蕴含有移频的意味存在,然而各种滤波器却有各自的使用方法及限制。

在解决EMI/RFI问题时,最常使用到的滤波器如图一所示,都是属于低通滤波装置。其中π型滤波器(π-Model Filter)是最有效率而简单的滤波装置,一般常用的整合性产品又分为CLC及CRC两种类型,如图二所示。

CLC滤波装置可以选择对主频率衰减影响最 小为考虑,其最主要是用在当系统内部的讯号在做传递时,当只需要对其高频的倍频谐波(Homonic)做滤波处理时,能使主频能量尽量保持原大小,而将高 频讯号滤除。而CRC类型的滤波器,则主要会使用在系统的接口端,可以具有能选择较佳阻抗匹配(Impedance Match)的特性,有效降低因为阻抗不匹配所造成的二次干扰问题。

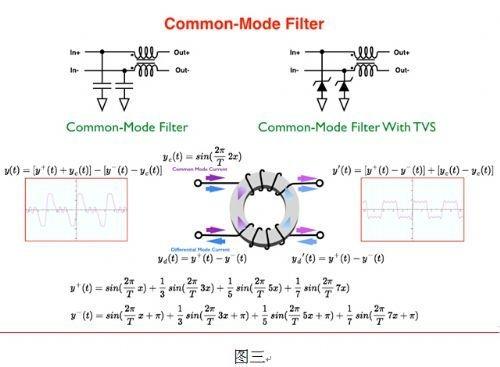

无论那种滤波装置,要考虑滤掉的频率能量是多或是少,还必需考虑讯号的倾斜 (Skew)及抖动(Jitter)问题来做决定,因此不一定是把所有的高频讯号滤掉越多才会越好,有许多时候适当的保留3倍频及5倍频甚至7倍频讯号能 量,会使得眼图(Eye Diagram)更佳。然而,在差动讯号(Differential Signal)的处理上,正端与负端的讯号必需相位差180度的完整讯号才能得到最佳的眼图。而来自电源及地端的偶数倍频谐波或是共模噪声 (Common-Mode Noise)都会造成差动讯号的失真,参考图三中左侧的讯号。

要解决这个问题,主要就是使用共模型式的滤波抑制器(Common-Mode Choke),利用小讯号在电感讯号抑制器中,共模讯号会被抵消的方式,来过滤掉共模噪声,如图三说明所示。然而使用图三中的共模滤波(Common- Mode Filter)装置,由于差模讯号上相当于也会看到了L型(L-Model)滤波效应,因此使用这种滤波器件必需同时看差模与共模的滤波频段,两者的滤波 效果是不同的。到此可以发现,以上两类型的滤波装置都是用来解决讯号上的噪声问题。而且,有许多机会是用在产品的接口端,那么静电放电的问题在此也不容被 忽视。

因此,晶焱科技整合了其系统级的静电防护技术与这些讯号滤波产品做了一个完美的结合,如图二及图三中含有TVS(Transient Voltage Suppressor)的滤波装置,就是用来同时有效解决静电及滤波的问题的产品。另外,在使用这些滤波器件时,所需注意的不再是电容的大小,而必须在意 讯号的传输损耗(Insertion Loss)以及反射损耗(Return Loss),在S参数中的这些信息才代表有多少能量的讯号可以传递或反射,藉此信息选择适合的主要频点及要滤波的强度。

在电源及接地部份,系统的印刷电路板(PCB, Printed Circuit Board)中的小讯号返回路径(Return Path),为EMI辐射的最主要磁耦极天线(Magnetic Diople Antenna)路径,。良好的多层板接地面设计虽然可以降低返回路径的面积,但是如果仅使用不具有减震效果的电容器,再加上在系统内未能设计出良好真实 的接地点位置,这样反而会将电源噪声带到了整个接地面,而造成了宽带(Broad Band)噪声。

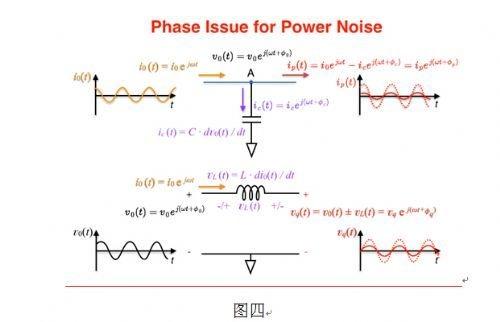

但是,如果使用RC减震器(Snubber),那么就必须要调整RC值到能过滤的频段,这又是另外一项艰难的任务。另一方面,由于主芯片 (Main Function Chip)的内部电路设计又会有倍频、除频等需求的设计存在。因此,许多的各种奇、偶倍频小讯号能量,就变成了噪声而载波在电源上。再经由系统上的电源及 接地设计,而辐射或传导到PCB的各个位置。而在这些繁多集成电路的复杂运作下,又造成这些噪声能量,在主芯片电源接点附近之电压、电流单频讯号不再是 90度(可用电容或电感降噪)或0度(电阻特性)的相位差。

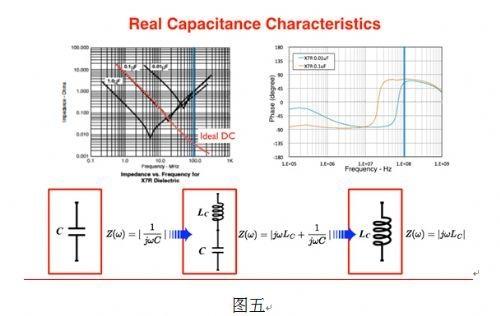

但是单纯的电容或电感的使用下,电压或电流小讯号仅能做90度的相位加减。但是,当电压电流相 位差不再是90度或0度时,那么使用电容或电感,有时反而使得一些单频噪声更加强,如图四所示是个复杂的迭加(Superposition)效应。此外, 电容的使用也必须注意它有一定的使用频段范围,在超过它的频率返折点后,它就变成电感了,如图五所示。而在频率返折点附近,也会有极点(Pole)问题存 在。晶焱科技为解决以上之问题,利用分支电流的特性,设计出具有能在宽带带范围中,同时侦测电压、电流小讯号,并能调变其间的相位差,而做出滤波减震芯 片。

除具有电源滤波效果外,也可以减低噪声传导到地的能量。并将其设计成电容之大小型式,以方便工程师在产品开发最后阶段的验证时,能够有除了电容以外的 最佳而方便的选择,以追求产品量产的时效性(Time To Market)。在可?式产品中的RFI问题,就如同在处理电源噪声问题一般。有些状况是:RF讯号原是用来接收使用,但它们一样会耦合到了电源端,而造 成部份其它的功能性芯片的失常;另一些情形是:一些功能性芯片(例如摄像头...等)的倍频讯号或电源噪声,耦合到Base Band或RF IC的电源、讯号或天线中,而造成这些芯片的功能暂时失效或错误。

欲解决可携式产品的电磁干扰问题,首先第一步须对PI的问题做初步的解析。对于电源及接地的布局,最好能针对各电源抽出各层次来与接地层做重迭审视, 对于一些返回路径确认是否己下了对的解决方案。另外,对产品中电源及接地布局,最好能使用模拟工具确认其阻抗特性(Z-Frequency Characteristics)之极点位置,要能尽量避开敏感的频段位置。其次必须确认产品讯号上的SI问题(如Impedance Match, Interconnection Bandwidth, Insertion Loss, Return Loss, Cross Talk, Propagation Delay...等)是否都已调校好,藉由量测工具确认问题点,选择合适的讯号滤波装置。在处理SI问题时,若有再发现一些偶数倍频的问题时,再回头确认 一下是共模问题或是电源及接地部份的问题,检验其来源,加上对的滤波对策。能够对产品的SI及PI做了完善的布局解析,并对各式滤波装置的应用特性有充份 的了解,选择对的滤波器件,这样对于解决电磁干扰问题就能事半功倍。

|

|