ARM Cortex M3系列GPIO口介绍(工作方式探讨

|

- UID

- 1029342

- 性别

- 男

|

ARM Cortex M3系列GPIO口介绍(工作方式探讨

一、Cortex M3的GPIO口特性

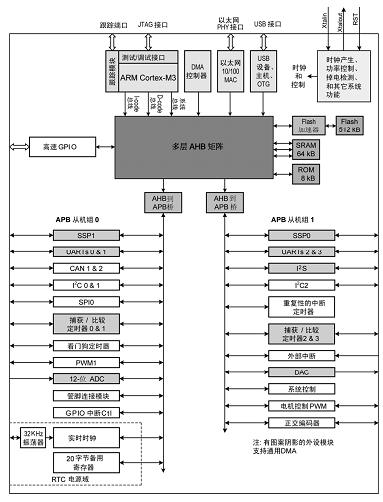

在介绍GPIO口功能前,有必要先说明一下M3的结构框图,这样能够更好理解总线结构和GPIO所处的位置。

Cortex M3结构框图 从图中可以看出,GPIO口都是接在APB总线上的,而且M3具有两个AHB到APB桥,GPIO则直接接在AHB矩阵上,这样可以减少CPU和DMA控制器之间的竞争冲入,获得较高性能。APB总线桥配置为写缓冲区,使得CPU或DMA控制器可直接操作APB外设,而无需等待总线写操作完成。 M3数字I/O功能:

高速GPIO口,其寄存器被移到外设AHB总线,可以字节,半字和字寻址。

位电平置位和清零寄存器允许单指令置位和清零一个端口的任意位。

所有GPIO口寄存器支持M3位带操作。

整个端口值可以用一条指令写入。

GPIO口寄存器可由GPDMA控制器进行访问,可以进行DMA数据操作,使之与DMA请求同步。

单个I/O口方向可以控制。

所有I/O口在复位后默认作为上拉输入。(Why?因为微控制器连接了很多设备,如果复位后作为输出,则由于控制器电平状态不定,可能会导致外围设备产生动作,从而产生不利影响,故复位后一半都作为输入状态。)

M3可产生中断的数字端口:

PORT0 和 PORT2 端口的每个引脚都可以提供中断功能;

每个端口上的中断可被编程为上升沿、下降沿或边沿产生中断;

边沿检测是异步的,因此可以在没有时钟的情况下(例如掉电模式)操作。使用这种特性,就无需电平触发中断;

可掉电唤醒;

寄存器为软件提供挂起的上升沿中断、挂起的下降沿中断和整个挂起的 GPIO中断;

GPIO0 和 GPIO2 中断与外部中断 3 事件共用相同的 NVIC 通道。

二、GPIO口的寄存器描述

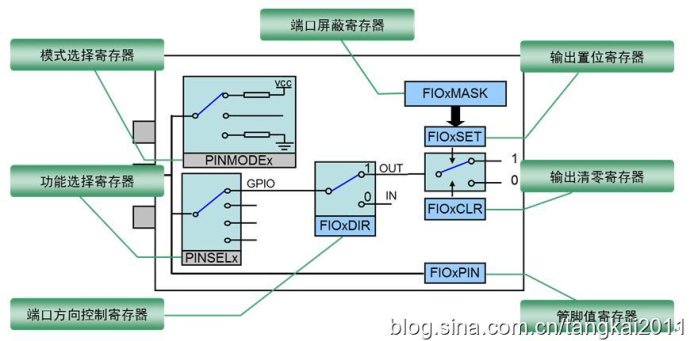

Cortex M3引脚的寄存器描述:

PINMODEx表示引脚模式选择寄存器,在使用前要配置好。

引脚模式选择寄存器位 PINMODEx | 功能 | 复位后的值 | 00 | 引脚使能上拉电阻 | 00 | 01 | 中继模式 | 10 | 引脚无片内上拉或下拉电阻 | 11 | 引脚使能下拉电阻 |

中继模式说明:当引脚处于逻辑高电平,中继模式能使能上拉电阻;当引脚处于逻辑低电平时,中继模式会使能下拉电阻,这样当引脚配置为输入且没有外部驱动时,能够保持上一个已知状态。

PINSELx:功能选择寄存器。用来设定PORT引脚的功能,当PINSELx各位为0时,才用作GPIO

端口。

FIOxDIR:GPIO口方向寄存器,单独控制每个端口管脚的方向,可作为字节(8位),半字(16位)和字长(32位)的数据进行访问。

FIOxMASK:屏蔽寄存器。任何写、读的操作只在该寄存器对应位为“0“时才有效。

FIOxPIN:管脚值寄存器。只要管脚不配置为ADC,其他所有方式都可以从该位读出端口当前的实际状态。注:如果读FIOPIN寄存器,那么不管物理引脚的状态如何,在 FIOMASK

寄存器中被“1”屏蔽的位将始终读出0。

FIOxSET:输出引脚的状态。写 1 使相应的端口引脚产生高电平。写 0 没有影响。读该寄存器返回端口输出寄存器的当前内容。只可以更改 FIOMASK 中为 0 的位,即非屏蔽位。

FIOxCLR:控制输出引脚的状态。写 1 使相应的端口引脚产生低电平。写 0 没有影响。只可以更改 FIOMASK 中为 0 的位,即非屏蔽位。 |

|

|

|

|

|