|

- UID

- 1029342

- 性别

- 男

|

摘 要: 给出了一种基于DM6446 处理器的视频运动车辆检测系统的技术实现方法,介绍了系统的硬件结构及软件设计思路。结合DM6446 双核处理器的特点,给出了处理器ARM 端与DSP 端通信及双缓冲区切换的具体方法。在视频运动车辆检测算法上,采用差异积累法对DM6446 实时获取的交通视频数据进行背景建模,用背景差法检测车辆运动区域,再结合Otsu 阈值化、形态学滤波及区域生长等算法,最终在DM6446 硬件平台上实现视频运动车辆的实时检测。实验结果表明,该系统具有良好检测效果。 随着现代交通运输业的快速发展,道路上的车辆日益增多,而伴随而来的交通拥堵、道路使用效率不高等问题却给日常交通管理带来了重重困难。融合了计算机、电子等现代高新科技的智能交通系统(ITS:Intelligent Transport System)提供了解决方法。

运动车辆检测是ITS 的重要组成部分,本文探讨了以TI 的TMS320DM6446(简称DM6446)为嵌入式开发平台的交通视频信息采集和处理系统的设计,通过分析实时交通视频序列,采用差异积累背景建模、Otsu 自动阈值选取、形态学滤波及区域生长定位等技术,最终实现交通场景视频运动车辆的检测。

1 系统硬件构成

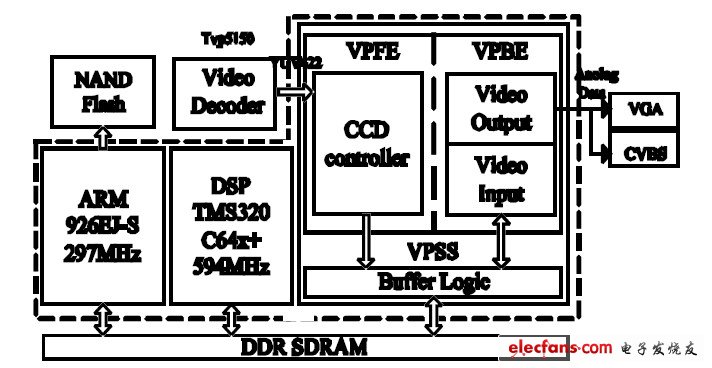

本系统选用的TMS320DM6446 是基于ARM926 和TMS320C64x+两个核心的、高度集成的数字媒体处理器。ARM926EJ-S 采用管道化流水线可以执行32bit/16bit 指令集,并提供了独立的16KB的指令Cache 和8KB 的数据Cache,可有效控制和管理外部中断、各种接口及外设。TMS320C64x+属TMS320C6000 系列高性能的定点DSP 处理器,集成了64 个32 位通用寄存器和8 个功能单元,硬件支持块循环操作,采用二级Cache 结构:L1 程序/数据Cache 和L2 存储/Cache.ARM 和DSP 共享外部256MB DDR SDRAM 存储器,64MB NAND Flash用于存放ARM 和DSP 代码。

系统硬件平台还包含视频处理子系统(VPSS)和众多外设资源。VPSS 是DM6446 中专门负责视频输入输出的硬件模块,由视频处理前端(VPFE)和视频处理后端(VPBE)组成,系统模拟视频信号经由TVP5150解码器解码成YUV422 格式的视频数据后传送给VPFE 的CCD 控制器,然后通过EMIF 接口将暂存在VPSS 内部Buffer 中的数据传送到外部DDR SDRAM中。VPBE 的屏幕显示(OSD)模块将视频数据以YCbCr形式提交给视频编码器(VENC),通过视频编码器输出到VGA 或CVBS 接口。本文处理系统的硬件拓扑结构如图1 所示。

图1 DM6446 系统平台硬件结构示意图

2 系统软件设计

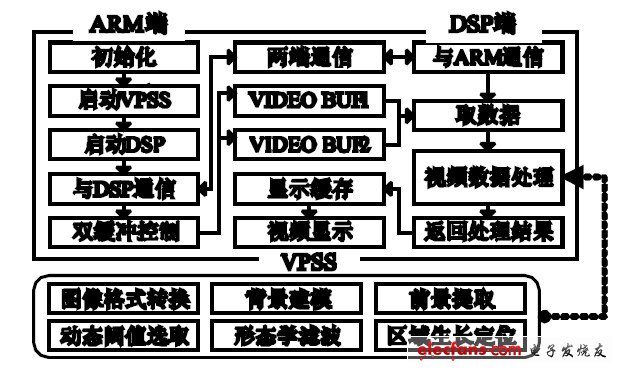

图2 示意了系统硬件平台软件处理模块的组成结构。如图2 所示,软件部分主要完成3 个任务:图像的采集与存放、ARM 与DSP 通信和视频图像处理。

图2 DM6446 系统平台软件模块构成框图。

ARM 端负责初始化系统并控制数据的采集和存放。系统初始化时VPSS 被配置为场模式,VPFE 负责将采集到的视频数据连续传送到内存缓冲区。由于ARM 端在向内存中存放图像时DSP 端不能同时读取,为了保证数据处理的正确性,本文采用双缓冲机制,即:设定两个各自连续的帧缓冲区VIDEO BUF0 和video BUF1,视频数据交替的向这两个区域缓冲刷新。

ARM 与DSP 两核之间的通讯通过内存共享和中断的方式实现。ARM 通过寄存器ARM2DSP0 向DSP发出中断信号,DSP 使用寄存器DSP2ARM0 给ARM发送中断信号。发中断的一方在中断信号发出前向共享内存填写命令,接收中断的一方在中断函数中读取命令,其他模块按照当前的命令执行相应任务。

视频图像的处理在DSP 核上进行,采集到的视频图像数据为YUV422 格式,算法处理时仅读取视频数据的Y 分量,紧接将视频数据进行差异积累背景建模、运动区域检测等操作以实现对视频序列运动目标的检测。最后DSP 负责将检测完的视频数据存放至固定显示缓存区,由VPBE 读取后显示。 |

|