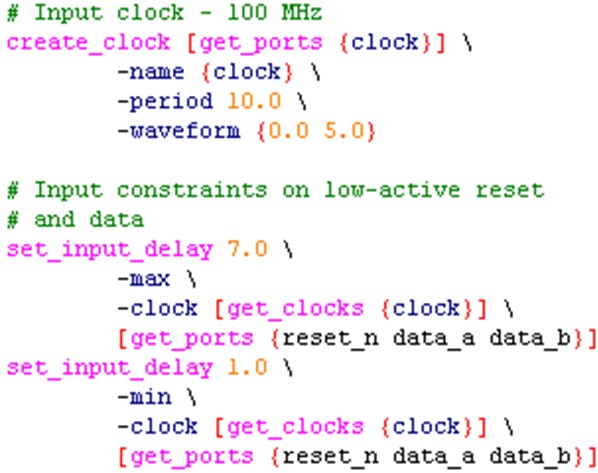

图6:SDC文件中约束外部同步复位信号

而大部分时候,输入到FPGA的复位信号是异步信号,在这种情况下,复位信号必须在内部先同步后再送达寄存器。如图7所示,现在同步寄存器位于FPGA内部。

图7:内部同步复位原理图

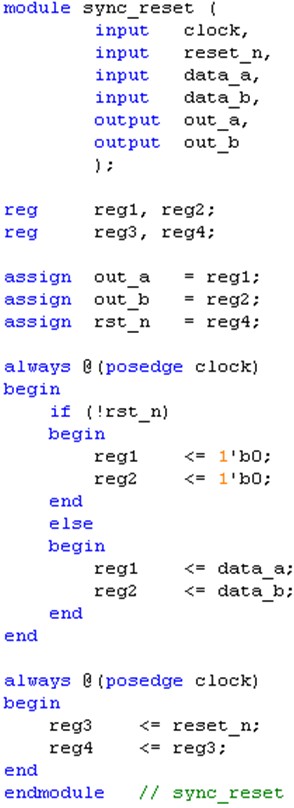

相应的,等效图7电路等效Verilog代码如图8所示。同样地,注意这里时钟沿还是唯一敏感列表。

图8:内部同步复位Verilog代码 SDC文件里的约束和外部同步复位类似,只是现在复位输入信号不能被约束,因为它是一个异步输入信号,所以它应该被施加一个伪路径约束,如图9所示,这样就可以避免这样的路径被系统认为是未约束的路径。

图9:SDC文件中约束内部同步复位信号

同步复位的另一个问题是图8中的同步寄存器的输入是异步信号,而常常有可能该异步信号的脉宽比较小(小于一个时钟周期)。一方面,这可以看作是一个缺点,因为异步信号同步的时候必须保证脉宽至少要一个时钟周期长,这样才能保证异步复位信号在第一个同步寄存器被捕获。另一方面,这又可以看作是一个优点,因为短脉宽增加了其抗噪声性能。这个异步输入上的一些虚假脉冲,如毛刺,很有有机会被第一个寄存器捕获,所以它们也就不会触发同步复位。在某些情况下,我们可能需要进一步增强抗干扰能力,可以让电路拒绝比如任何小于n个时钟周期的脉冲触发同步复位。这其实也非常有益于对异步输入的复位信号进行去抖动。为了做到这一点,应将电路作出以下修改,如图10所示。

图10:经过脉冲扩展的内部同步复位原理图

在许多设计中,可能不止一个时钟信号。在这些情况下,每一个时钟域都应该采用一个独立的复位同步电路。如果设计中使用了PLL,那么使用的时候有些地方需要格外注意。如果采用PLL的输出时钟来创建同步电路,那么这些时钟域将不会被复位,直到PLL锁定和PLL的输出时钟已经稳定。另外值得一提的是,如果PLL使用了复位信号,那么这个复位信号没有必要同步到PLL的输入时钟。一个异步复位即可用来复位PLL。同样,PLL使用复位,当PLL的输出时钟域都使用内部同步复位的时候,将进一步拖延这些时钟域同步复位置位。这个问题我们将在同步化的异步复位中再讨论,而且我们将看到这个问题被同步化的异步复位很好的解决。 |