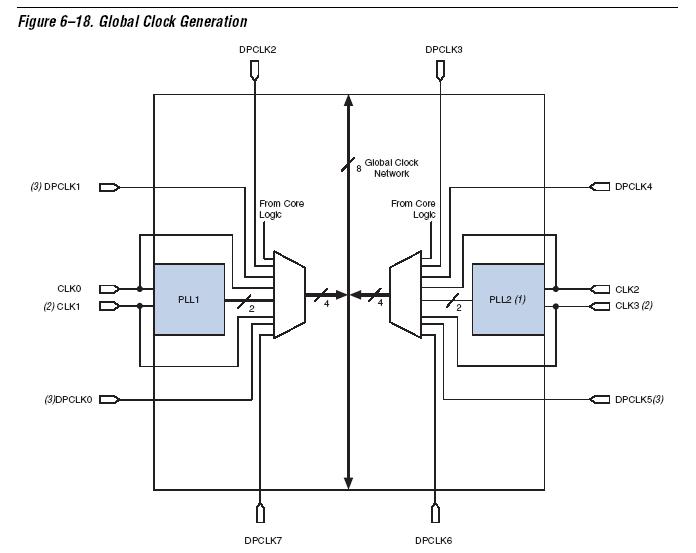

下面再看看cyclone器件的内部全局时钟网络的分配,8个全局时钟网络,左右各4个。而PLL1的输出c0,c1和CLK0/1以及DPCLK0-3(复用的时钟管脚)或者内部的逻辑可以使用左边的4个全局时钟网络;PLL2的输出c0,c1和CLK2/3以及DPCLK4-7(复用的时钟管脚)或者内部的逻辑可以使用右边的4个全局时钟网络。PLL输出作为外部时钟的e0是不会(也没有必要)分配到全局时钟网络的。

就拿左边的来说,可以使用4个全局时钟网络的信号其实不少,它们之中到底谁使用有限的全局时钟网络呢?说白了,都是可以由你掌控的,当然了,在你不管它们的时钟会有一个缺省的状态。

如果Setting--Fitter Setting--More Setting…里的Aoto Global Clock开启时,Quartus II在实现时会根据内部逻辑的实际情况自动分配全局时钟,就是说谁占用全局时钟网络软件说了算(一般系统的时钟和复位信号会占用全局时钟网络)。当然了,你也可以关闭它,然后自己来分配,这时你可以到Assignment Edit里Global Signals进行分配。然后你可以到编译报告里查看Fitter—>Rescource Section—>Global…里的信息。

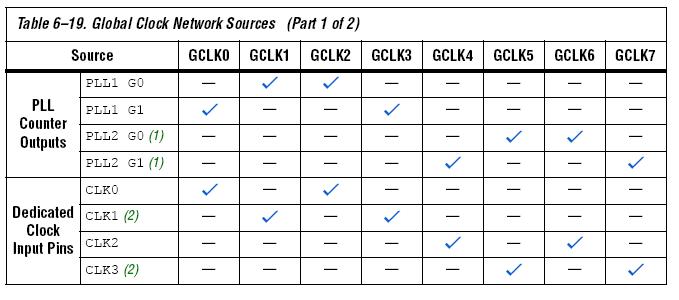

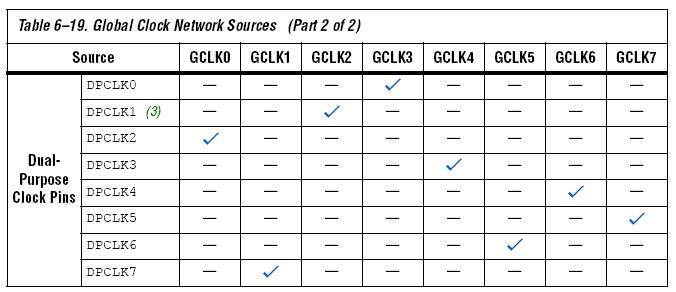

另外还有一个值得注意的地方,下面两个图示出了可以占用全局时钟网络的信号它们实际可以占用的全局时钟网络资源。比如PLL1的输出c0只能使用GCLK1或者GCLK2,c2只能使用GCLK0或者GCLK3。

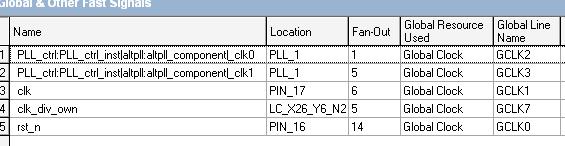

拿一个实例来看看,我们有一个CLK1输入的时钟信号clk,这个时钟信号clk同时是PLL1的输入,产生两个PLL输出c0和c1。系统本身有一个复位信号rst_n。此外,我们内部逻辑产生一个时钟clk_divown,在Aoto Global Clock开启的情况下,我们得到了下面的全局时钟网络的分配结果。

PLL的c0分配到了GCLK2,c1分配到了GCLK3,PLL的输入时钟即CLK1的输入clk分配到了GCLK1,它们都分配到了规定的全局时钟网络内了。其次,clk_div_own和rst_n随机分配。

这个例子中的全局时钟网络对于我们的使用还是绰绰有余的,但是一个大的系统,时钟交错,高扇出的信号层出不穷,那么对于全局时钟信号的掌控就需要格外小心了。

说白了,对于设计者来说,最重要的是要做到一切尽在掌握。 |