|

- UID

- 852722

|

2. 1. 2 寄存器文件的错误保护

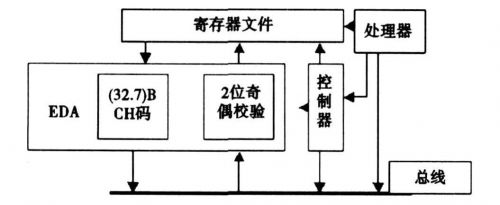

采用1、2奇偶校验, 同时采用( 32. 7) BCH 校验和进行容错。寄存器文件错误保护原理如图2所示。

2. 1. 3 触发器的错误保护

采用TMR三模冗余的方式进行容错。触发器错误保护中,通过比较器来进行表决以输出正确的数据输出。TMR ( Tr ip le-M odu la r- Redundancy)的原理是将同一份信息保存在三份物理存储空间中。读取的时候比较三份内容, 如果不完全相同, 就取两个一致的值为真值。在控制器通过总线向内存写入数据(WR 有效) 时, 每一比特数据通过三态门同时写到三个对应的比特存储单元中。当总线向内存请求数据( RD有效) 时, 三份同时存储的内容到达比较器, 比较器逻辑按照前述规则输出数据内容及是否发生2 /3判决的标记。这是一种在系统结构上通过增加冗余资源的方法来掩盖故障造成的影响, 使得即使出错或发生故障, SoC芯片的功能仍不受影响, 仍能够正常执行预定任务的技术。

| | 图2 |

触发器的错误保护中采用TMR三模冗余寄存器的方式进行容错。触发器错误保护中, 通过比较器来进行表决以输出正确的数据输出。这种容错设计中, 当有一个以下冗余寄存器出错时可以输出正确结果, 当两个以上的冗余寄存器出错时就会输出错误的结果。触发器文件的错误保护原理如图3所示。

| | 图3 |

2. 2 多IP核间通信的可靠性研究

IP核间通信总线的稳定性直接关系到整个系统的可靠性。我们对IP核间的通信进行了研究, 加入一些检错模块, 保证通信时数据的正确性, 进而提高整个系统的可靠性。

| | 图4 |

IP核间通信采用AMBA 2. 0 AHB 和APB 片上总线协议, 增加一个AMBA Controller模块对整个AMBA 片上通信进行监控,通过检错信号反馈信息对该模块采取进一步的保护措施, 当出错时, 使整个流水线重启, 保证通信数据正确, 错误数据被抛弃。检错算法采用2位奇偶校验。

IP核间可靠性通信原理如图4所示。

2. 3 嵌入BIST电路, 检测IP核的工作状态

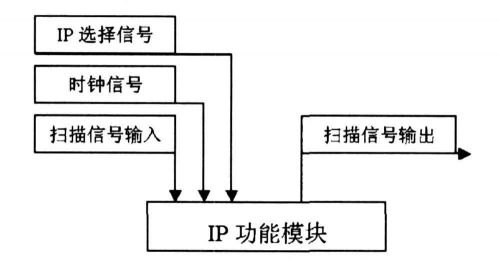

B IST ( Built- In SelfTest) 是一种芯片内建自测试, 即在芯片上集成一种自我检测的电路。基于DFT思想, 在片上集成了一种B IST模块来提高系统的可靠性。在芯片内增加产生激励和做测试分析的电路, 使芯片不但能完成逻辑功能, 还能在外部给定测试方式命令时进行自我测试分析, 并输出结果。这种结构的电路既不需要准备测试码, 也不需要专门的测试设备。电路中包含有测试码生成部件、扫描测试电路和测试结果输出部件, 如图5 所示。

| | 图5 |

SoC 芯片在上电运行中自动对自己的运行状态进行监控, 并通过扫描输出信号即时返回该IP功能模块的状态信息, 在其它控制模块中再根据这些状态信息采取相应策略保证SoC 的可靠运行。

3 结束语

对于SoC 芯片, 可靠性是首要考虑的问题, 基于多IP复用SoC 的设计技术, 重点解决处理器的可靠性、多IP核间通信的可靠性、IP核工作异常状态研究, 可以进一步提高SoC 芯片的可靠性。

近几年来本单位根据智能终端产品特点, 进行智能终端专用SoC 芯片研发, 在SoC的设计过程中充分考虑了其可靠性, 加入了非常全面的可靠性算法, 采用奇偶校验、TMR(三模冗余)寄存器、片上EDAC、流水线重启和强迫CACHE 不命中等多层次容错机制来提高SoC的可靠性, 已在FPGA 验证平台上得到验证, 并进行SoC 芯片流片和批量生产验证, SoC 芯片的可靠性得到大幅度提高, 验证本方法可行, 具有很好的推广价值。 |

|