|

- UID

- 852722

|

随着移动通信的普及,移动通信设备商之间竞争也更加激烈;各大通信巨头为了抢夺市场,不断提高基站的性能,降低基站的价格;低噪声放大器是基站接收机的第一级,看到低噪声放大器位于接收机的最前端,因此对基站接收机来说,低噪声放大器是十分关键的部件,它直接影响到整个接收链路的信噪比,对提高基站灵敏度有决定性影响。 安捷伦公司的A TF54143 是一种增强型伪高电子迁移率晶体管,不需要负栅极电压,与耗尽型管相比较,可以简化排版而且减少零件数,该晶体管最显着的特点是低噪声,并具有高增益、高线性度等特性,他特别适用于工作频率范围在450 MHz ~6 GHz 之间的蜂窝/ PCS/WCDMA基站、无线本地环路、固定无线接入和其他高性能应用中的第一阶和第二阶前端低噪声放大器电路中。

1.1 晶体管模型低噪声放大器

通常会在源极加电感来增加稳定性,稳定性设计对于任何放大器都是必需的,没有设计成绝对稳定的放大器不能应用到产品中去的;影响低噪声放大器稳定性的因素有很多,其中源极电感是其中之一。

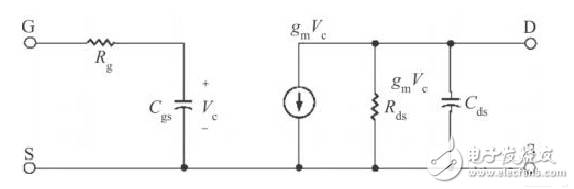

图2未加源极电感的FET 等效原理图

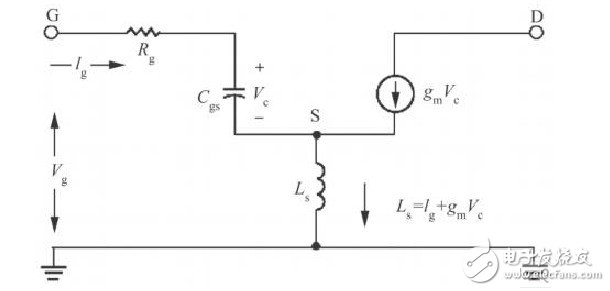

图3 添加源极电感的FET 等效图

加入源极电感不仅改善稳定性,也能改善输入输出匹配与噪声系数,是设计低噪声放大器非常重要的方法。

1.2 电路原理图

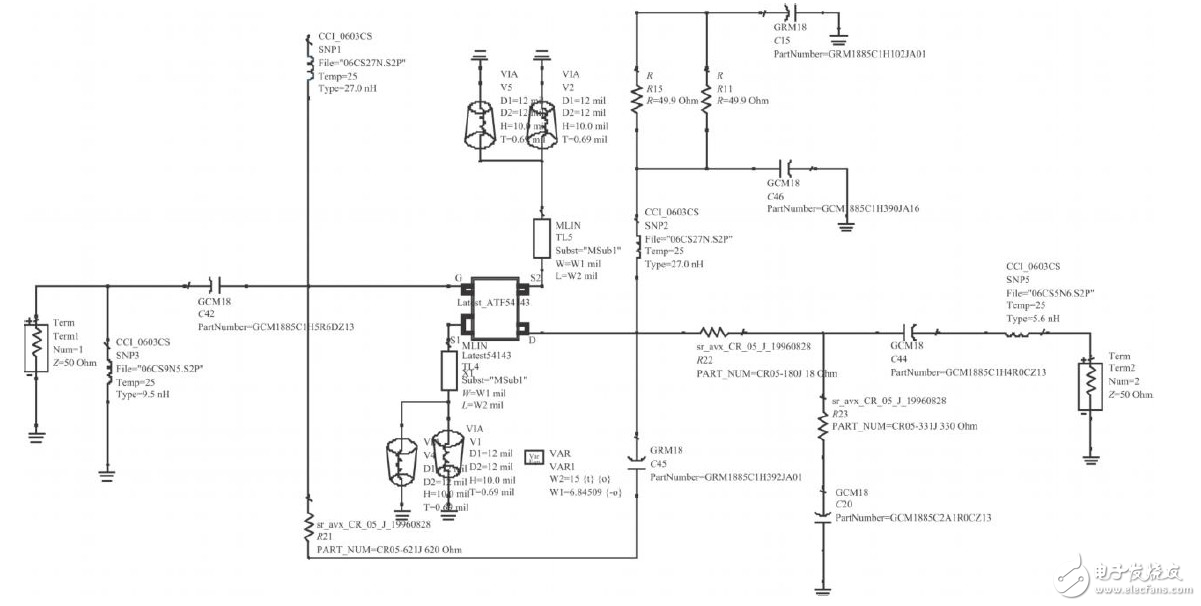

根据原理图,利用ADS 对电路进行S 参数仿真,为了提高仿真的准确性,电路元器件都采用了厂商提供的等效模型,同时将Rogers 的板材特性参数代入微带线模型中。图4 是用于ADS 的仿真原理图。

图4 仿真原理图

通过ADS 仿真及最后的实际电路测试,我们发现该低噪声放大器能够较好的满足设计要求。图5是实际测试结果图。图中可以看出,实际测试数据与仿真结果比较一致。

低噪声放大器是基站接收机中的关键器件之一; 本文采用安捷伦公司的先进设计系统与A TF54143 ,通过对噪声系数与输入回波损耗的折中设计,进行共轭匹配,成功设计出低噪声放大器。其工作频段的性能参数为:噪声系数为0185 ,P1 dB约为16 dBm ,输入回波损耗大于20 ,输出回波损耗大于14 ,增益保持在18 dB 以上。得到了最终的版图并且对其进行测量,并经过高低温与差异性测试,证明其完全能应用到实际产品中,目前准备应用于杭州某通信公司的产品中。 |

|