项目背景及可行性分析

项目名称:基于压缩参考帧的单FPGA芯片视频压缩系统项目的主要内容:本项目设计一种不需要外部存储就能在单片FPGA上进行视频压缩IP核。视频压缩算法采用MPEG-4框架,但引入压缩参考帧技术,使得在Virtex-4LX25器件上压缩QVGA分辨率(320×240)视频不需要外接存储芯片。

目前的进展情况:系统的整体设计与系统框图已经完成,系统硬件平台调试通过,MPEG-4部分模块设计已经完成。

2,项目关键技术及创新点的论述

项目关键技术:适合FPGA资源特点的高效性能运动估计模块;基于硬件资源复用的参考帧压缩。

创新点:通过复用变化、量化、编码、反变化、反量化硬件模块,并合理安排时序,以极少的硬件资源实现压缩参考帧。

3,技术成熟性和可靠性论述

基于Virtex-4LX25的MPEG-4的intra帧编码器已经运行成功,消耗资源很少;资源消耗极多的动估计模块的仿真显示,目标器件资源充足;时序安排规划表明,资源复用完全可行。这些都说明了整个系统框架的可行性。

项目实施方案

1.方案基本功能框图及描述

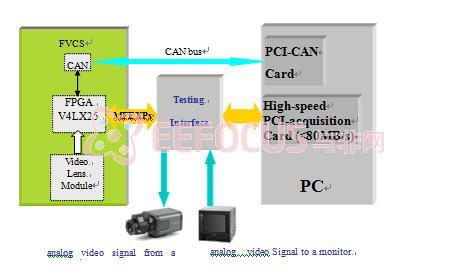

图1.中的FVCS为压缩参考帧视频编码器(CRF)的硬件运行平台,该平台上有一颗Virtex4-LX25芯片,并且带有三组通用IO口和一个CAN总线接口。一组通用IO口和Video Lens Module连接以获取原始数字视频信号。其它两个IO口可以连接测试接口(Testing Interface),进而连接模拟视频源、监视器和PC机。可见,整个系统构成一个灵活且易于调试、测试的综合FPGA之视频IP开发环境。

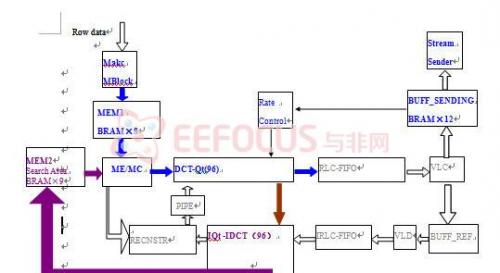

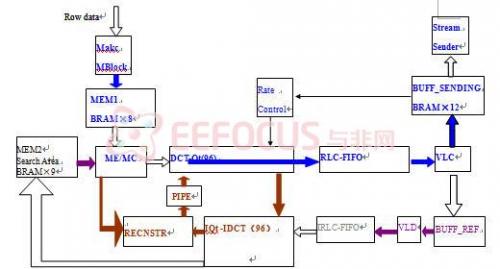

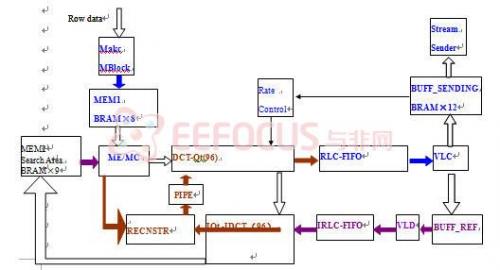

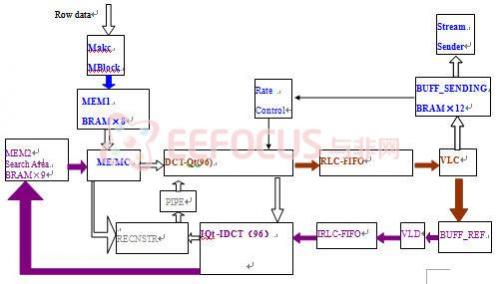

图2-1~图2-4则为FPGA中的CRF的模块框图;并且反映了压缩过程中,数据流在内部模块的流动状态。其中蓝色箭头为原始图像数据流,褐色箭头为第一次重构数据流,紫色箭头为第二次,也就是压缩后的参考帧恢复数据流。

图2-1.运动估计编码新宏块,IQ开始重构参考宏块

图2-2.DCT开始压缩参考宏块,并启动被压缩的参考帧的解码

图2-3. IQ开始解码压缩参考帧

图2-4. 解码压缩参考帧,压缩参考帧被缓冲

2.方案实施过程中需要开发的模块

由于MPEG-4的Intra模块已经开发完毕,并且整个系统基于硬件复用的原则,剩余的模块只有运动估计补偿模块(ME/MC)、重构模块(RECNSTR)和变长解码模块(VLD)

3.系统最终要达到的性能指标

该系统需要在Virtex4-LX25芯片上完成QCIF的高压缩比视频压缩。 |