《玩转IP core》之十七:看客做饭,CDMA接收机的同步

|

- UID

- 863084

|

《玩转IP core》之十七:看客做饭,CDMA接收机的同步

常言道:“南甜北咸,东辣西酸”,不同地方的人有不同的口味。那么,如果您请朋友吃饭最好可得看人家的口味点菜。您非要请正宗的四川人吃潮汕打冷,或者请地道的广东人吃重庆江湖菜,估计这个效果不会太好。同样的道理,在进行设计的时候,也应该多考虑整个系统的要求,才能很好的平衡面积与速度,获得比较好的结果。这就对结构工程师提出了比较高的要求,不能“乱点鸳鸯谱”。

世界上的系统万万千,不同用户的要求更是千奇百怪,显然《系统篇》里面不可能把所有的系统设计都讲明白。鄙人写这一篇 的目的,只能在于举例子、说思想。列位只有做到领会思想、举一反三才能成为好的听众。子曾经曰过:“温故而知新,可以为师矣”。老衲说:“思想是永存的”。

咱们就愚公之家----开门见山好了。这一讲里面会介绍CDMA系统的同步部分,这不是重点。关键是,大伙儿会看到同样的算法,在终端和基站侧由于系统用户数目不同,会有不同实现。这是给大家的一个启示:不能因循守旧,要与时俱进。

这里说的CDMA是针对一种调制方式“码分多址”,而不是针对特定的系统。这个CDMA可以是IS-95,可以是W-CDMA,当然也可以是自定义的系统。

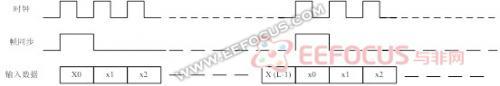

假设系统输入的数据,以帧同步开始排序,为x0,x1,…,L为一帧的数据量,如图。导频码的信息已知。一般接收机系统里面会采用过采样技术,也就是说一个码的变化周期,会有多个输入数据,这样可以保证采样进度。

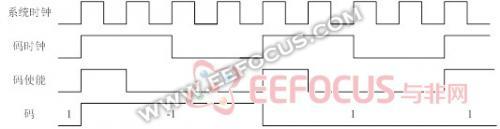

所以,框图里面用码生成器代表CDMA里面很重要的导频码的产生。(IS-95里面是Walsh码 + m序列,W-CDMA里面是Walsh码 + Golden码,这些就不详细介绍了。如果真的用,看看协议好了。)导频码生成器有三个输入:帧同步、时钟和相位设定,作用是在帧同步开始,按照时钟产生设定的相位开始的一些列的“码”。这里面的码,是一个比特的二进制数,表示“+1”(二进制“0”)和“-1” (二进制“1”).这些是约定,后面都照此办理。

一些系统会有插入导频,或者说导频不是时间连续的。这种情况,可以采用外部的时序使能来控制导频码生成器或/和我们后面的同步搜索单元,来处理。不是本讲的重点,不详细描述。后面,全部按照连续导频来介绍。

系统输入数据的图中,时钟是采样时钟,不是码时钟。码的周期与时钟关系如下图。顺便说一句,导频码生成器原则上的时钟,是由系统时钟分频出来的。但是,考虑到《统一行动听指挥》一讲的介绍,用系统时钟产生使能信号驱动导频码生成器比较合适。这是多时钟系统的一般技巧,不去多说。

用了这么多篇幅介绍背景,本不是老衲的本意。但是,实在没法子。一旦遇到介绍系统设计的话题,不介绍背景,那没几个人能听得明白。贫僧不想说天书,就不得不讲背景知识,就这还节略了不少呢。

CDMA的同步是接收机系统的核心,其作用是搜索和同步空间信道的“多径”,用于后面的RAKE解调。(这里面一堆名词,大家不必太在意,不影响后面听讲。我说这些是用来堵一些专家的嘴的。正月初三包饺子,“堵小人嘴”。面试的时候可以用来唬人。但是,别吹大了,牛皮不破才好。)这一讲里面,我们只计算信道的“延时功率谱”(别急,后面有计算公式。我冒充一次算法工程师,把公式给大家。)。“延时功率谱”就是一堆和时延有关的、高高低低的数据,如下图的样子。后面再如何处理,那是后话,反正最后能正确解调空中的信号,完成通讯。鉴于我们的主题,在座列位不是做通讯算法的,在此按下不表。

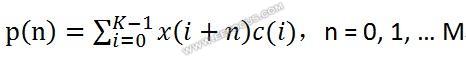

计算延时功率谱的公式是

其中,K是算法规定的累加长度,和搜索精度有关;M为规定的搜索长度,与假设的小区半径以及多径时延有关。

无论对于基站还是终端,表达公式是一样的。并且,我们假设基站和终端需要的同步周期是一致的。也就是说,对以一个用户需要在规定时间内,至少进行一次同步搜索过程。(但是,在分析了基站与的终端不同特点之后,具体的系统结构却是大相径庭了。这是后话,先剧透一下下。)

先来看看基站侧的特点:多用户共用。也就是说,基站必须支持多个手机用户的同步搜索能力。这叫我们想起来,上一讲的多路复用的“批发价”了。对头,让我们再去批发一个同步搜索。

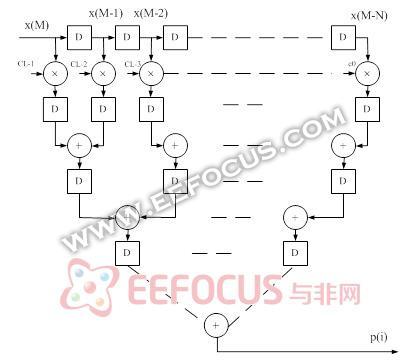

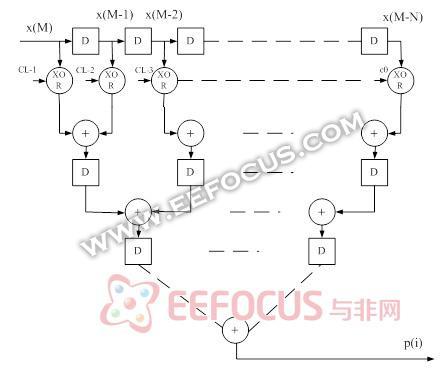

一同观察计算公式,似乎有几分相识吧。好好想一想。提示一下:FIR滤波器。对了,这个FIR滤波器的算式是一样的,理论上这叫做“匹配滤波器”。但是,由于导频码不是对称的,所以无法采用对折方式简化这个结构。拷贝那节的结构,改改信号名称,就成了如下的结构图:

心急的孩子,总是会犯错啊。兄弟,这里的导频码是一比特的这个特点,您没考虑简化一下?真正好的结构如下:

其中,由于一比特的特点,所以乘法变成了XOR操作;而且,由于XOR操作几乎不占时间,所以节约了一层的时延。这些都是雕虫小技,不登大雅之堂。

这个“匹配滤波器”占用面积相对是很大的,对于单个用户而言,浪费很大,真心地不划算。但是,我们这就开始批发成多用户,堵住一些人的嘴。

对于基站的接受信号,配置不同的导频码序列,数据注入若干个,输出的p(i)就是要求的延时功率谱。

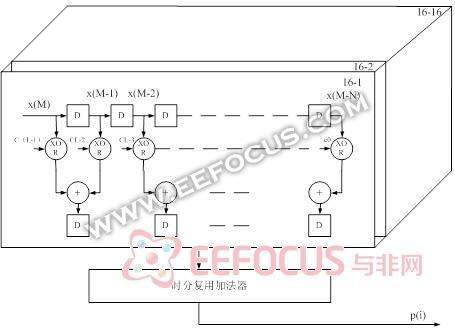

还有值得提到的是:在延迟了两到三级之后,实际上加法器就可以复用了,因为根本用不着那么快的时钟了。还有,前面也不一定要真正的L长度。可以流水线完成L的若干部分,例如十六分之一,再时分复用完成后面的16次加法。这样可以进一步地节约匹配滤波器的面积,见下图。到此为止,用了十六分之一的资源,大伙做到了单通道的匹配滤波器。

在追加一点基础知识,搜索周期T远大于搜索需要的时间L。一般,T是秒级的,而L是10毫秒级的。也就是说,一个匹配滤波器,可以支持100个左右的用户。这基本上是一个基站需要支持的用户量的极限了。掐指一算,假设搜索长度为400,那么平均每个用户的加法器开销大约0.3个,够节约的了吧。

花开两朵,各表一枝。下面讨论手机里面的事情。首先,手机里面不能有多用户了。谁见过哥俩一起用一个手机,同时打电话的?可怜的我们,找不到批发价这个便宜了。没关系,“猫有猫路,鼠有鼠道”,我们自有办法。

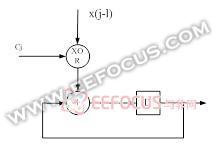

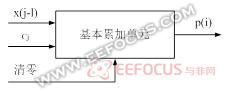

还是观察公式,这个公式的最直接的实现如下图,就是一个基本累加器的变型。我们把这个单元成为基本累加单元。

下来,我们通过时分复用的戏法,利用一个基本累加单元算出所有的演示功率谱。基本思想是,每次算一个相位,逐次算完全部的功率谱。对于一个相位而言,x的输入位置是前一个x的地址加一,而导频码产生器则需要复位。这样计算L次之后,就获得了完整的演示功率谱。这个结构就是著名的“滑动相关窗”。

下来就需要计算,一组这个单元是不是能满足搜索长度的要求。如果不满足,那么就要几组分别计算几段相位的。无论如何,再算上控制部分的花销,这个手机侧用户所需要的面积绝对大于基站里面的情况。

这正是:同步公式大家懂,终端基站各不同。莫道不知系统路,变化之道自从容。

正式内容结束了,下一周会给大家一些程序风格上的建议。

鉴于这是本讲座正式内容的最后一讲,和大伙儿多扯点犊子。时光荏苒,日月如梭,转眼间就要和广大观众分别了,实在有些留恋啊。实际上,IP core的内容博大精深,鉴于这个讲座的规模,不可能给大家一一介绍的。

这个讲座里面的例子不能说不重要,但是老衲更希望诸位掌握的却是讲座始终在宣传的精神:“用变化的手法,依据系统的需求,灵活设计结构”。套用《叶问》的台词:“天下没有普世的结构,只有最适合的结构。”

在工程中,经验固然重要,你设计过USB 2.0接口肯定对你设计USB 3.0接口有帮助。但是,电子工程师的不幸或者说幸运在于,你遇到的系统要求是一直变化的。说不幸,是你不可能一直依靠以前的程序,吃老本;说幸运,是永远有新的需求,你不会被“兔死狗烹”。这里面的道理,大家体会吧。

--------

《玩转IP core》之一:我们的目标是ASIC

摘要:具体到一个产品里面,到底是采用FPGA还是ASIC,这个问题是多方面确定的。简单说,如果产品出货量小、时间紧、生命周期短,那么FPGA比较适合;反之就建议ASIC。但是,也不是完全绝对的,就像很难说少林和武当那个更牛一样。

《玩转IP core》之二:所见非所得

摘要:Verilog语言是由Gateway设计自动化公司的工程师于1983年末创立的;VHDL语言诞生于1983年,1987年被美国国防部和IEEE确定为标准的硬件描述语言。这个古人也“古”不到哪里去。上板砖!

《玩转IP core》之三::统一行动听指挥

摘 要:现在我们正沿着PCB数据大道,走向芯片大厦----就是大家眼前的巨大的、银色的大厦。我是本次旅行的导游,敝姓十,大叫可以叫我十导。路途之中, 为了大家不感到无聊,本人先给大家略略介绍一下,什么是数字电路的时钟。数字电路中,时钟是整个电路最重要、最特殊的信号。

《玩转IP core》之四:踏雪寻熊---面积与速度的协调

摘 要:具体到我们的FPGA/ASIC设计,这个“鱼”就是面积,而“熊掌”时钟频率(速度)。能不能很好的协调面积与速度的关系,是衡量一个数字逻辑设计 工程师能力的一个重要标准。在本讲座的第二篇里面,会说明各种单元模块的不同面积和速度的基本解构;在第三篇中,则会通过例子,介绍如何在系统中很好综合 考虑两者的关系,选择比较合适的实现解构。

《玩转IP core》之五:测试向量生成

摘要:在不考虑电源输入的前提下,在我们系统/板子上,能够不依靠其他外界输入而产生输出信号的器件有木有呢?当然有,而且必须有,那就是大名鼎鼎的晶振了,用来产生我们说过的、对以系统极端重要的系统时钟信号。

《玩转IP core》之六:程咬金的三板斧--系统基本结构

摘要:今天我们开始进入本讲座的第二部分:单元篇。大家将会发现,我们在基本单元设计里面,也就是三板斧:查找表、时分复用和流水线。但是,我们比程大将军稍稍高一点,我们会把这三招糅合,能产生变招。

《玩转IP core》之七:一个计数器引起的思考

摘 要:设问句:在进行一个计数器单元设计之前,我们需要什么前提条件呢?首先,需要功能描述(一个计数器嘛,不就是在不是复位“RST”的状态,每来一个时 钟内部/输出加一吗?还描述什么啊?磨洋工吧?----“非也,非也”,这个还是要描述一下。至少我们需要知道一下计数器的内部位数吧?也就是,计数器加 到多大回到0。)另外,就象我们在前面“菜谱”那一讲里面说过的,需要了解系统需要的时钟频率。

《玩转IP core》之八:小学一年级水平,加法器的结构

摘要:工程设计里面有一个原则:从简单做起。这里面还有一个小故事,今天就不讲了。现在,我们先瞧瞧最简单的一个比特位宽的加法器:半/全加器。全加器的输入为三个一比特的信号a0、a1,还有低位的进位c0;输出也是两个一比特的信号:结果s和进位位c1。

《玩转IP core》之九:小学二年级水平,乘法器的结构

摘要:大伙儿已经通过两次讲座,了解了计数器和加法器大体结构。大家不难发 现,同样的一种功能,可能由于需要、工作频率和代价的不同要求,存在若干种不同的结 构。这些结构如何选择,实际上是一个艰难的选择。这些选择,很多时候都是靠一个工程师的经验(我们老年人也就靠这个混口饭吃了。要不就被“长江后浪推前 浪,前浪死在沙滩上”了)。

《玩转IP core》之十:除法器的结构

摘要:如果各位在加法器和乘法器里面可以欣赏到了变化多端的话,那么在下不得不很遗憾的通知诸位:除法器里面大家只能看到“自古华山一条路”。不是 我保守,是除法这个东西的本性。用《数学分析》里的说法,加法和乘法都是线性运算满足交换律的,除法是非线性运算不满足交换律的。这是数学上的根子,可以 用来唬人。

《玩转IP core》之十一:非线性求值的孤独九剑,CORDIC方法

摘要:现在来个“师夷长技以制夷”,给大家画画CORDIC的流水线(因为是小数运算,假设实数“1”为十六进制的全1,实数值就可以折算了。这是普遍的技巧,不详述。)。还有一个小技巧就是由于每步的放大作用,公式里预先收缩了一把。

《玩转IP core》之十二:电路串串香,D触发器链

摘要:今个儿寡人给大家讲点有“理论”的:CRC校验(循环冗余校验 码,Cyclic Redundancy Check)和编码器。CRC校验的目的就是看接收的一串比特和原来发射的是不是一致,有没有接收误码。CRC在编码界的春典,就是“gCRC16(D) = [D16 + D12 + D5 + 1]”和“1 0001 0000 0001 0001”。给大家一个口诀:“延时触发串一串,遇到一字砍一段。输入牵来异或算,输出导出入口看。”

《玩转IP core》之十三:简直的层层叠,FIR滤波器的串联实现

摘要:今天我们继续信号处理的行程,给大家介绍FIR滤波的串行实现。却说“请介绍FIR滤波器和IIR滤波器的差别”,这可是一道非常典型的面试题。这道题目类似于《哈利ˑ波特》里面那个“分院帽”的作用,当然这个题目里面没有宝剑。

《玩转IP core》之十四:我的地盘我做主,锁相与分频

摘要:在做设计的时候,谁都希望片子的输入时钟是稳定的、可靠 的,并且和我们系统的采样频率是一致的。这是最理想状态。可惜啊,希望是丰满的,现实是骨感的。很 多时候,情况并没有这么理想。这种时候,就需要我们自己调节系统时钟,达到系统工作的目的了。不是大伙儿“无知者无畏”,是不得不为啊。实际上,在很多通 讯系统中,对于系统时钟的调节都是不可避免的。

《玩转IP core》之十五:国球与其它,输入输出介绍

摘要:我们现在正式为《第三篇:系统篇》剪彩(哗哗哗,掌声响起来,我心更明白…)。在这一部分里面,会在更高的层次上,分析设计问题。大伙儿不仅 仅能看到《单元篇》里面的各个部件的应用,而且会发现系统绝对不是单元的简单的搭积木。在整个讲座里面,“变化”是永远的主题。

《玩转IP core》之十六:来个批发价,多路数字中频系统设计

摘要:数字中频主要分两种类型:数字上变频(DUC)和数字下变频(DDC),它们的主要功能是相反,但原理和实现的方法是十分相似。由于FIR滤波器里面讲的是下采样的例子,这里也就以数字下变频作为例子,这样匹配。

《玩转IP core》之十八:磨刀不误砍柴工,程序的风格

摘要:“代码风格和规则”这个问题,很多人看来不是十分重要。但是,我问问大伙儿几个现象,看看是否遇到过?过了三个 月,读不懂自己的程序的,有木有?看别人代 码,赶脚不如自己重写的,有木有?做C代码的,竟然能看懂你的程序的,有木有?调试的时候,感觉是老虎吃天----无从下口,有木有?如果有,以老衲的经 验,多多少少和“代码风格和规则”有些瓜葛。

------------------

如果你从事FPGA研发,或者你对IP core设计感兴趣,欢迎关注《玩转IP core》系列技术讲座,每周三加菲博士与你不见不散,如果针对本讲座有任何技术问题欢迎与加菲进行技术互动可以加入QQ群(FPGA交流圈:23294742),或者去交流区提问:《玩转IP core》交流区

|

|

|

|

|

|