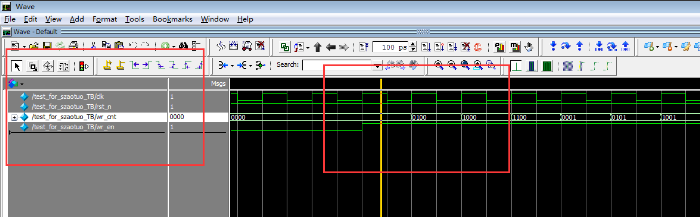

5.然后添加信号,仿真,run 500ns

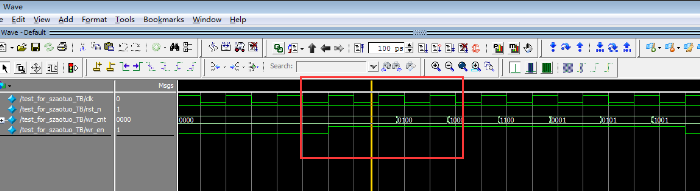

虽然,clk和wr_en是同时上升沿,但是cnt的输出晚了一个时钟周期。

综合后的仿真:vo(verilog网表)+testbench+仿真库模型

接下来看看时序仿真是怎么样子的

三:时序仿真:注意我这里没有添加约束,即这个仿真时在没有时序约束下的布局布线的仿真

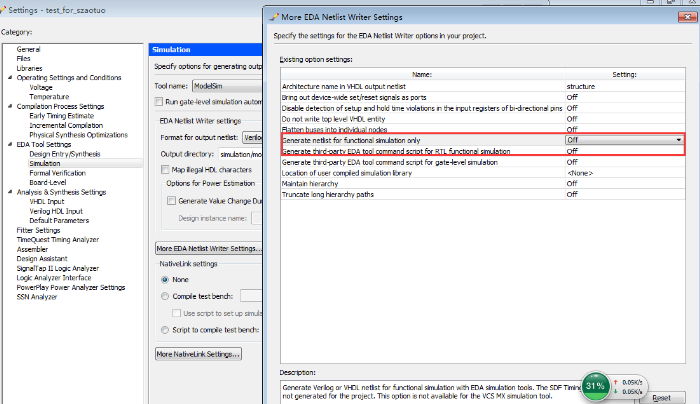

1.关闭仿真工程sim2,回到quartus,做出一个设置

2.在综合后的仿真,我们有一个设置为on,现在我们改为off,这样,除了生成网表vo文件,还会生成布局布线后的延时文件sdo文件

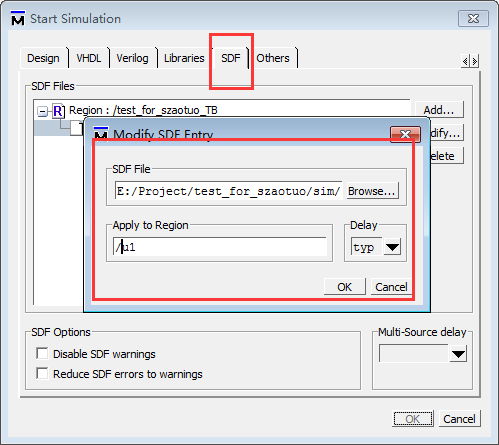

3.建立sim3文件目录,将vo和sdo和testbench拷贝到sim3,建立sim3的modelsim工程

和综合仿真多了一个地方,就是sdf那里添加sdo文件,apply to Region那里是testbench的例化的文件,我例化为u1

综合仿真时1个clk的延时,这里不只一个clk延时,可以清楚的看到3个仿真的结果。

时序仿真:vo网表+testbench+仿真库+sdo延时文件

总结:

学会了综合后的仿真:需要哪些文件,以及一般流程。

学会了时序仿真:需要哪些文件,以及一般流程

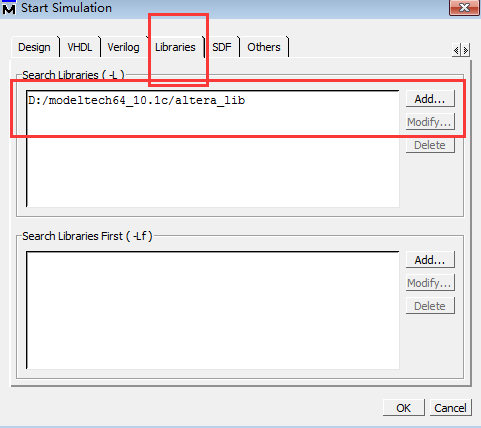

在即使有用altera IP 核的仿真,只要在仿真的时候,设置好那个library的搜索路径就可以了,因为我之前已经编译了,在启动的时候,那些就是资源库了,设置好路径就可以了。 |