史上最全经典设计案例:基于AES加密算法的保密通信系统设计,完整软硬件协同方案

|

- UID

- 863084

|

史上最全经典设计案例:基于AES加密算法的保密通信系统设计,完整软硬件协同方案

背景与意义

在被称为“信息时代”的今天,“信息”的价值越来越受到人们的重视,甚至被视为国家和社会发展的重要资源。互联网技术、通信技术的发展在带给我们获取信息便利的同时,也为一些受限信息、保密信息的泄密提供了机会。因此,发展信息安全技术是目前面临的迫切要求,正如知名安全专家沈昌祥院士呼吁的那样,要像重视“两弹一星”那样去重视信息安全。信息安全是一门综合、交叉学科,它综合了数学、物理、通信和计算机等诸多学科的长期积累的知识和最新发展成果。目前在信息安全领域人们所关注的焦点主要有密码理论与技术、安全协议理论与技术、安全体系结构理论与技术、信息对抗理论与技术、网络安全与安全产品等几方面。

数据加密是信息安全的重要手段,2000年l0月,美国国家标准与技术研究所( NIST )宣布由比利时人Joan Daemen设计的Rijndael算法为先进密码标准算法(AES)。该算法是一种迭代型分组密码,设计简单;与公钥密码算法不同,没有复杂的乘法运算,并行执行度高,加解密速度快,易于实现,灵活性强。可以预见,随着AES取代3重DES成为事实上的标准,该算法必将广泛应用于我国电子商务等领域的互联网数据加密业务,为我国信息安全的发展提供强有力的保障。

用硬件芯片实现加密算法及产生与之相关的密钥是当前的趋势,因为数据封装在芯片中,与当前常用的纯软件加密相比,信息不易被非法读取或更改,有较高的物理安全性。FPGA以其自身所固有的特点——既具有硬件的安全性和高速性又有软件的灵活性和易维护性,已经成为分组密码算法硬件实现的热点研究方向,与以往的主流硬件(如DSP芯片、单片机)实现加密方式相比,具有低成本、高速度、保密性强等优点,与ASIC相比具有设计灵活、成本低、周期短等优点。另一个明显的优点在于:在对时间代价和空间代价的取舍上,基于FPGA实现的加密技术提供了多种实现方案,分别对时间代价和空间代价有不同的偏重,有利于在各种应用环境中进行优化。

系统描述

2.1 系统的总体设计

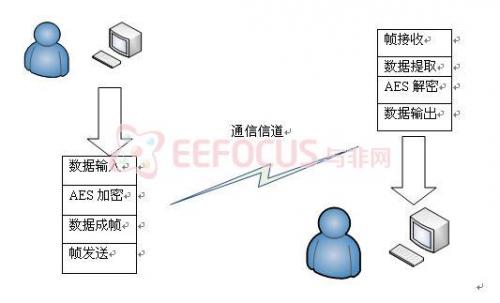

本系统框图如图2-1所示,信息源来自PC机,待发送数据经AES加密、数据成帧后发送,由信道传输到另一通信终端。接收端将接收到的帧进行数据提取、AES解密并将解密的信息显示在PC机上,从而实现了基于AES加密算法的保密通信。

图2-1 基于AES加密算法的保密通信系统框图

本系统采用了有线和无线两种通信方式来实现基于AES加密算法的保密通信。用硬件描述语言VHDL在FPGA数字逻辑层面上实现AES加解密,通过UART这种有线通信实现PC机与终端、加密终端和解密终端的信息通信。为了系统的可扩展性和构建良好的人机交互界面,设计了通过PS/2键盘输入加密密钥,并将其显示在LCD上。在软核MicroBlaze上,采用C语言可以容易地实现AES加密算法,并且软核支持SPI总线,能够灵活方便地控制射频芯片CC2420,使系统具有信道选择、地址识别、自动CRC校验功能,使系统更加安全、通信误码率更低。再用滑动开关做辅助,实现不同功能模式间的转换。

2.3 系统架构

2.3.1 FPGA硬件实现AES加解密

原理框图如图2-2所示:

图2-2 FPGA硬件实现AES加密算法的有线通信原理框图

数据通信信道都是串口线。加密端通过UART接口从PC机接收数据,当接收够16字节(128bit),或不足时能自动补零成128bit后送给硬件AES加密模块。加密完成后可将密文返显到PC机上,以便观察AES加密对传输信息的影响,同时通过开发板上DTE接口向解密端输出数据。解密端将解密出来的信息显示在PC机上。AES加解密算法所需要的密钥key由键盘输入,并在LCD上显示出来。必须保证两终端key相同才能保证正常通信。 |

|

|

|

|

|