时钟设备设计使用 I2C 可编程小数锁相环 (PLL),可满足高性能时序需求,这样可以产生零 PPM(百万分之一)合成误差的频率。高性能时钟 IC 具有多个时钟输出,用于驱动打印机、扫描仪和路由器等应用系统的子系统,例如处理器、FPGA、数据转换器等。此类复杂系统需要动态更新参考时钟的频率,以实现 PCIe 和以太网等其它诸多协议。时钟 IC 属于 I2C 从器件,需要主控制器来配置内部 PLL 逻辑,其控制逻辑可以写入微控制器内。作为 I2C 主机,微控制器将配置写入时钟 IC 的内部易失性存储器并控制 PLL。因此,可以通过板上 MCU - IC 组合进行系统时钟频率的动态更新。可编程微控制器为高性能时钟 IC 提供控制逻辑能力,通过减少板载 IC和板上走线使整体设计更加紧凑,并降低最终物料成本。

操作理论

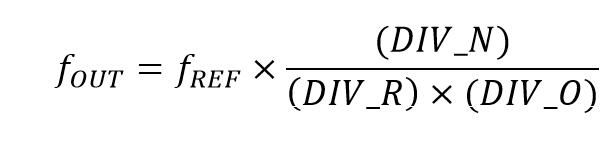

图 1 为高性能时钟设备的基本 PLL 架构。该设计使用比例因子为 PLL 输出端口提供时钟合成。最终输出频率的基本公式为:

· fREF 为输入参考晶体频率(在多数应用中通常为 8 MHz 至 48 MHz)。

· DIV_R(DIV_R1 和 DIV_R2)是输入频率参考的分频因子。此类分频器名为预分频器。

· DIV_N 为小数 N 分频因子。

· DIV_O(DIV-O1、DIV-O2、DIV-O3 和 DIV-O4)为输出前的后分频因子。

时钟 IC 的重要特性之一就是通过 I2C 接口实现运行时可编程。通过可编程功能,用户可以更改设备的易失性存储器内容以进行即时更改。只需使用适当的 I2C 指令,就可以通过主控制器实现用户配置文件的即时编程功能。

设备的非易失性存储器还可以存储预定义的多用户配置。用户可以使用频率选择 (Frequency Select, FS) 功能以选择其中一个配置。该 FS - 位为设备中可用的 CMOS 输入引脚。FS 引脚应用 N - 位外部 CMOS 信号,然后内部选择存储在非易失性存储器中的一个配置文件,这个配置文件同样也被复制到了易失性存储器,PLL 则输出不同的信号。

同时,微控制器通过 I2C 提供数据来控制高频时钟。使用微控制器的优点是,它具有不同的通信外设和通信协议,如 I2C、SPI、UART、蓝牙、ZigBee 等,使得系统能够以主从配置将数据传输到其他微控制器,也可以使用一个自定义的应用传输至安卓和 iOS 设备。此外,微控制器还配有各种 IDE 工具用于简化设计。这可以更好地证明使用 I2C 指令来配置 PLL 参数、编写并验证定制应用程序是合适的。 |